写文字之前,两个背景交代一下:

1.前文讲过USB3.0 的基础知识,可以先了解一下。

2.关于知识体系框架图(设计,仿真,测试),先有个概念。

言归正传。

1、Pre-Layout(先期布局

需要信号完整性工程师评估USB 接口摆放位置是否符合。是否符合取决于链路的情况,也就是链路评估。

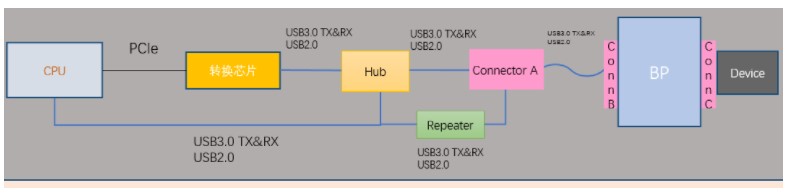

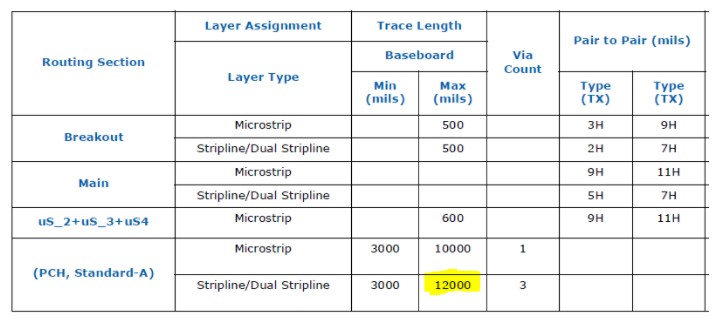

关于USB的链路,先要搞清楚USB 的拓扑结构,一般来自于前文中所说的4种拓扑结构之一。下图为一个综合的链路形式:

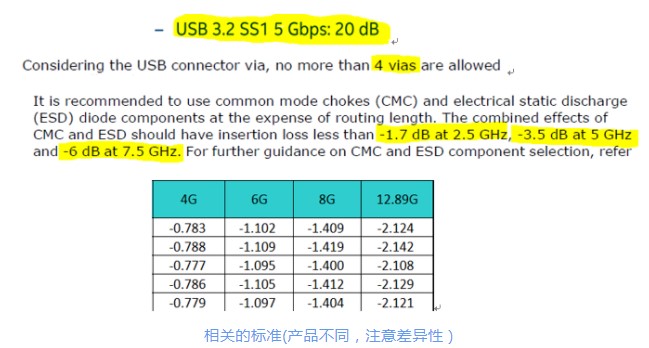

举个例子,选用简单的一种拓扑结构来做一种推算:

1.根据USB接口位置,预估线长为Y。

2.链路阈量。

4 dB (Package)+ 2 dB (PTH Connector)+ 0.3 x 4 (Via) + 3.5 dB (CMC&ESD) = 10.7 dB

(20-10.7)/0.9 =10.33 inches

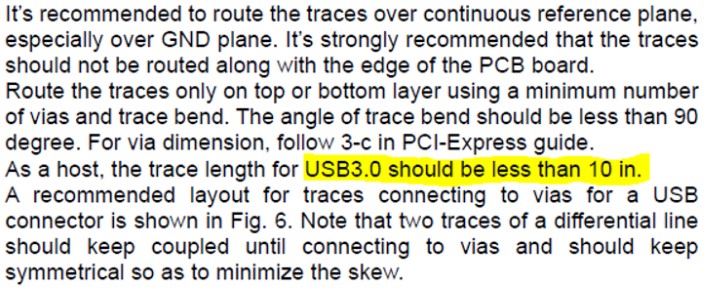

所以有些芯片DG给出的参考值 10 in。

有的小伙伴立马举手,说:我看到有些DG给出的是12 in。

这个是因为板材的区别(FR4 & Mid Loss)。

线长的最大长度除了受板材因素的影响,还有叠层和铜箔,都会影响。

2、版图检查

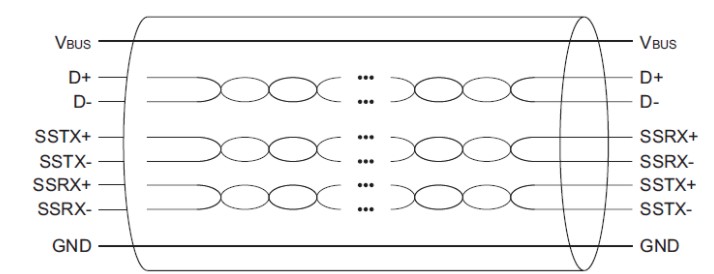

1.我们需要关注的信号是哪些,USB3.0信号图:

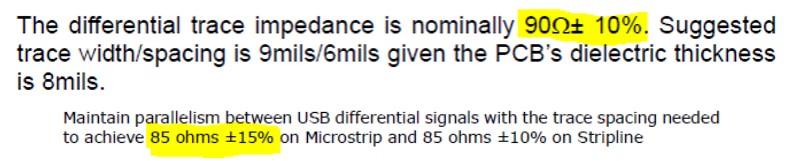

2.信号的阻抗:

阻抗的值根据产品链路的实际情况,做好阻抗匹配。

3.Layout

列举部分,以产品设计的checklist为准。

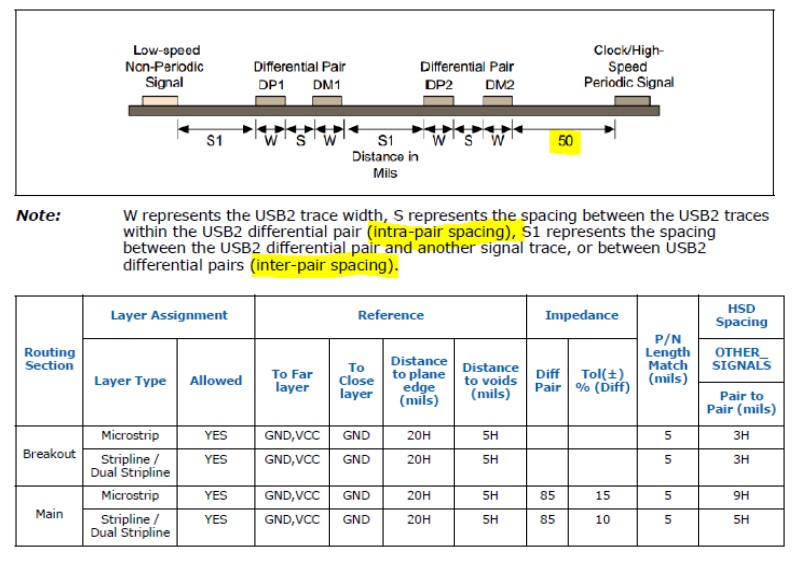

分清楚 Intra-pair spacing & Inter-pair spacing

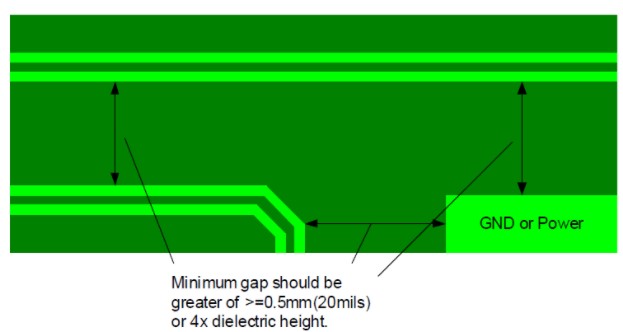

重读Design guide 发现有意思的一点:

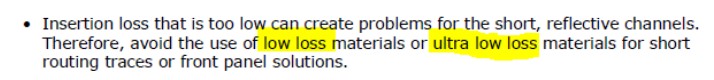

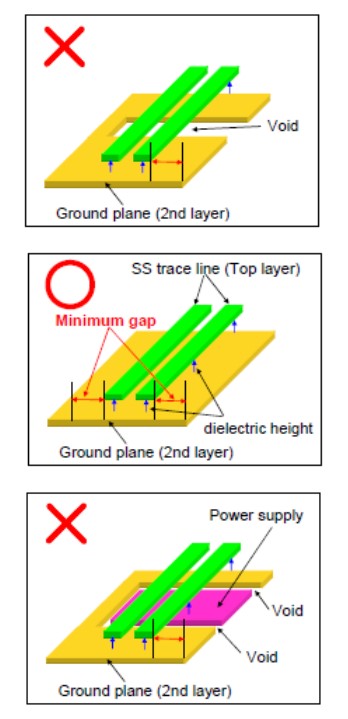

参考层完整性:

注:参考平面的改变,要加stiching via

避免串扰(Crosstalk)

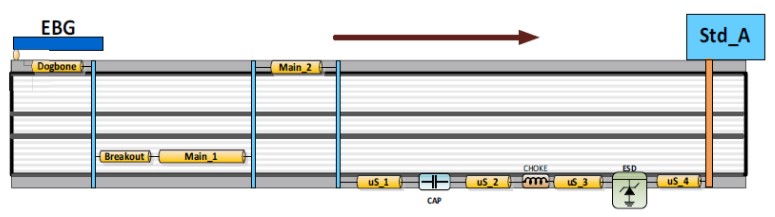

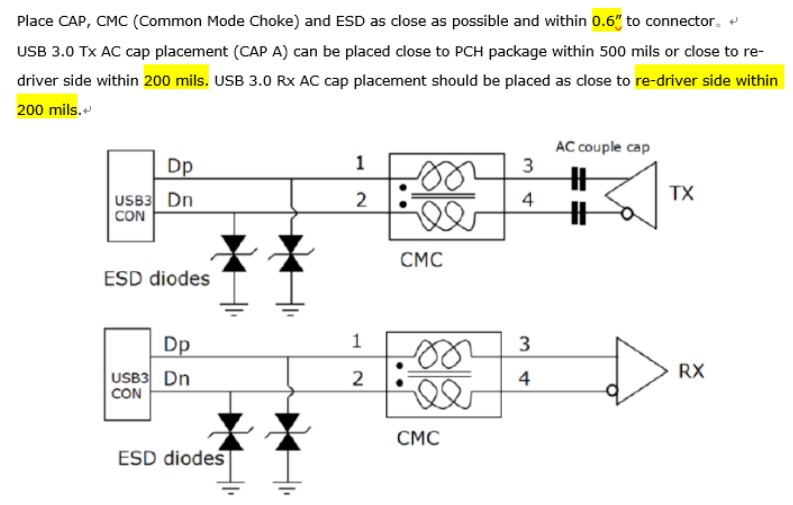

4.链路上器件的摆放:

关于CAP位置摆放标准,之前有做过相关的仿真,只要不摆放在链路的中间位置,尽量靠近发送端或接收端摆放都可以。

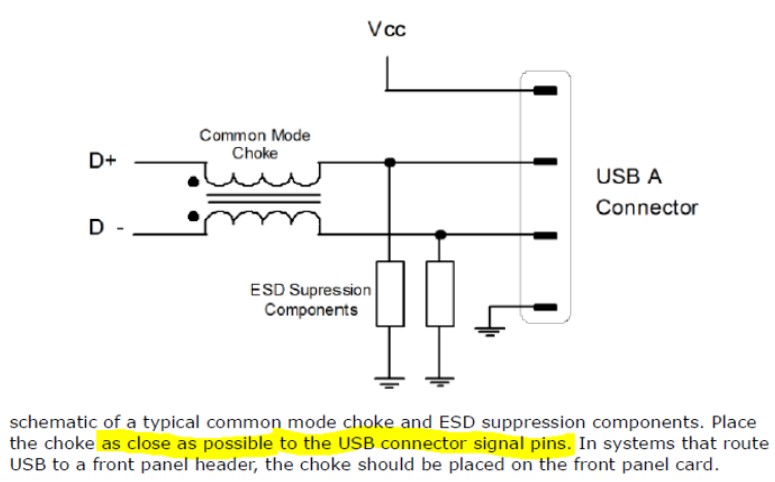

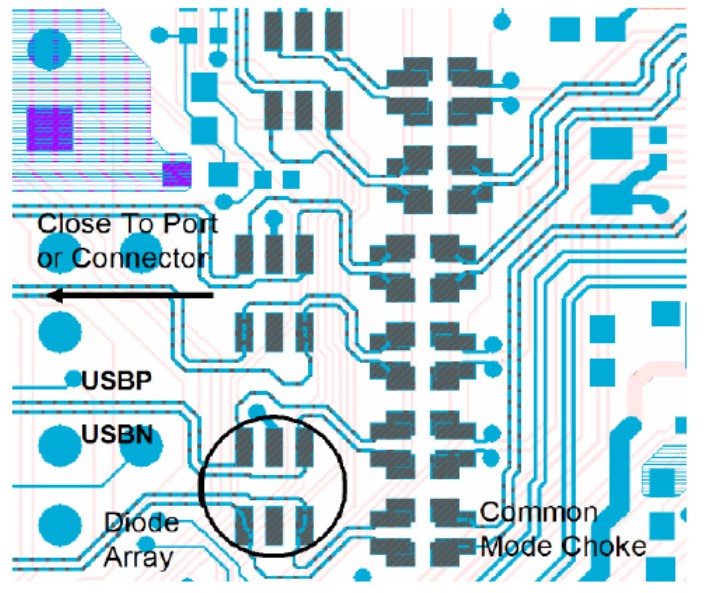

CMC(Common mode chokes)

ESD diode加在USB 信号路径,增大了寄生电容,影响了信号质量。版图设计可以参考如下优化。同时注意器件摆放层,减小stub。

5.电源部分:

电源部分的Power fill按照1.5 A 的阈量预估。电源部分牵扯到USB droop和IR drop的测试。还有电源路径的PDN的知识点。这里面就不做展开。

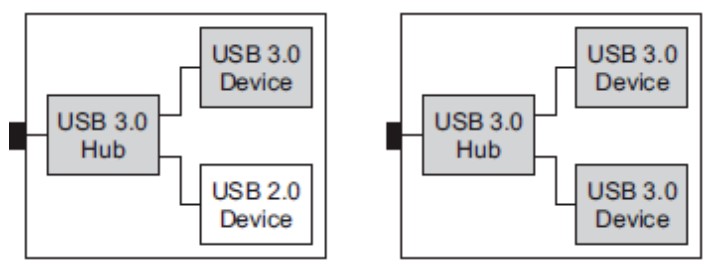

6.Hub部分:

Hub有USB3.0&USB2.0之分

7.Repeater(Re-driver&Re-timer)

摆放位置也没有明确说明,也是尽量靠近终端。

一般来说,就是调节均衡的设置,改善信号的上升时间和眼高的幅值,就不展开说了,参照使用手册。

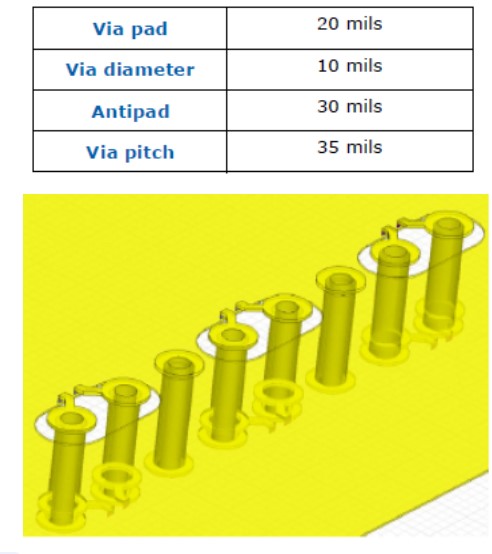

8.Differential Via

阻抗突变,注意优化。

3、总结

这边只拿一个简单的拓扑结构进行梳理,其他的链路中有redriver ,经过Hub转换,有Cable连接等各种的情况,不同的拓扑结构,具体情况分别评估,这里只做个抛砖引玉,就不一一展开了。

审核编辑:刘清

-

ESD

+关注

关注

48文章

2018浏览量

172888 -

USB接口

+关注

关注

9文章

700浏览量

55615 -

寄生电容

+关注

关注

1文章

292浏览量

19219 -

USB信号

+关注

关注

0文章

6浏览量

6509 -

CAP

+关注

关注

0文章

16浏览量

2080

发布评论请先 登录

相关推荐

信号完整性工程师眼里的USB信号该做什么?

信号完整性工程师眼里的USB信号该做什么?

评论