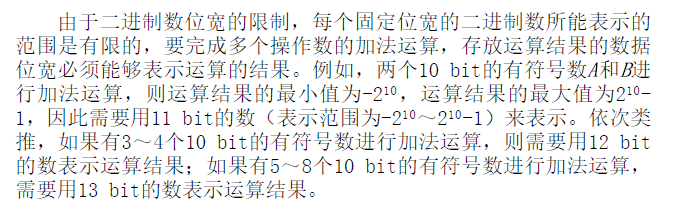

加、减 使用补码时,加减法可以统一,因而对加减不加区分,对有无符号也不加以区分。

为了不丢失进位,M位+N位时,设M>=N,则结果需要M+1位储存结果

图源:Xilinx FPGA数字信号处理设计:基础版 (杜勇),下同

当多个数据累加时,显然多一位存储结果,结果能够表示2倍(无符号数);当拥有3-4个操作数时,结果的最大值为4倍的单个操作数表示的最大值,因而增加2bit即可;类似的5-8个操作数,最大为8倍,因而增加3bit即可

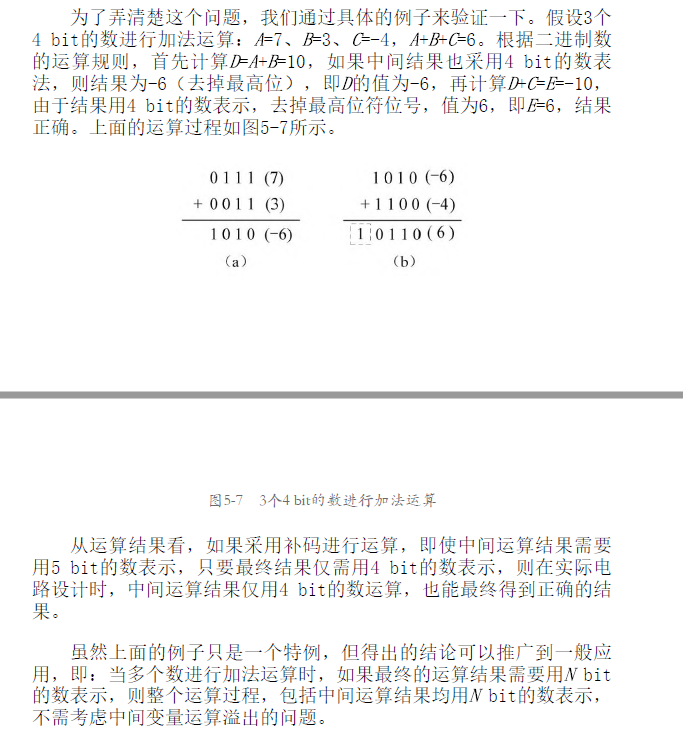

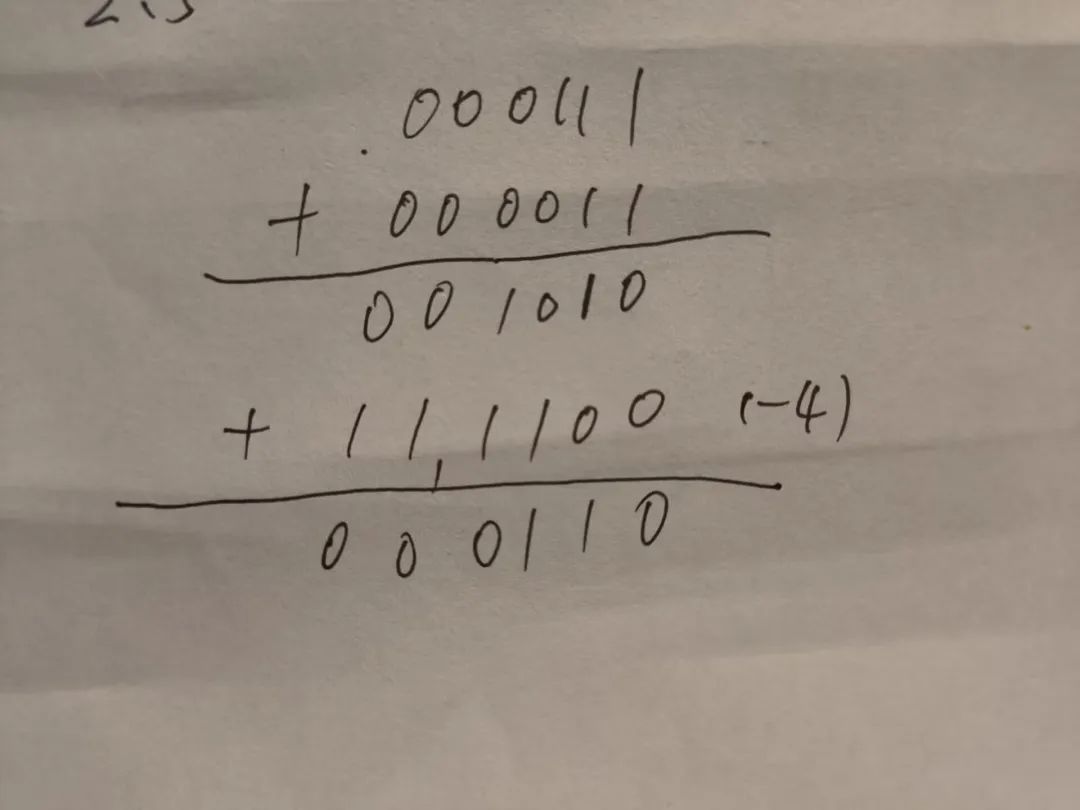

另一方面,当计算结果能够被约束时,不加证明地,存在一个结论:多个数相加,若结果需要Nbit即可,计算的中间值也只需Nbit

上面的计算过程若按照6bit运算过程如下,结果是一致的

2、乘法

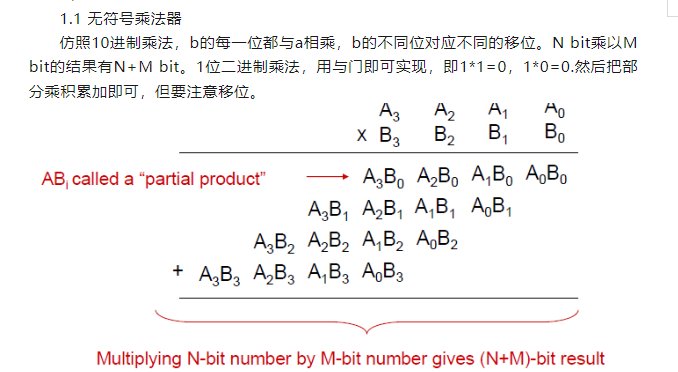

对于无符号数,N位*M位将得到N+M位的结果。可以直观的证明,如下图移位相加,N*M将移位(M-1)次,从而至少有(N+M-1)位,若加法出现进位,还需要额外1bit,共(N+M)位

有符号数,最高位需要表征符号,同样进行无符号乘法,再确定符号。因而N*M的有符号数,可以看成(N-1)*(M-1)的无符号数相乘,结果需要N+M-2位,还需要增加符号位,因而总共需要N+M-1位。

3、除法

除法更为简单,M/N,对于整数而言,N的绝对值大于等于1,因而商最大和M一样,只需要M位就行。

4、more

当结果位宽不够,会进行截断,带来丢失精度的计算结果。

审核编辑:刘清

-

FPGA设计

+关注

关注

9文章

428浏览量

26499 -

Verilog

+关注

关注

28文章

1345浏览量

110045

原文标题:verilog 整数四则运算的位宽考量

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

雾盈FPGA笔记之(二十五)六位数四则运算计算器(1)整体结构及设计思路

雾盈FPGA笔记之(二十九)六位四则运算计算器(5)数码管显示

雾盈FPGA笔记之(三十)六位四则运算计算器(6)小算法实现BCD转二进制

雾盈FPGA笔记之(三十二)六位四则运算计算器(8)算法实现加减乘除

西门子S7200四则运算指令表分享

利用simulink设计四则运算仿真模型

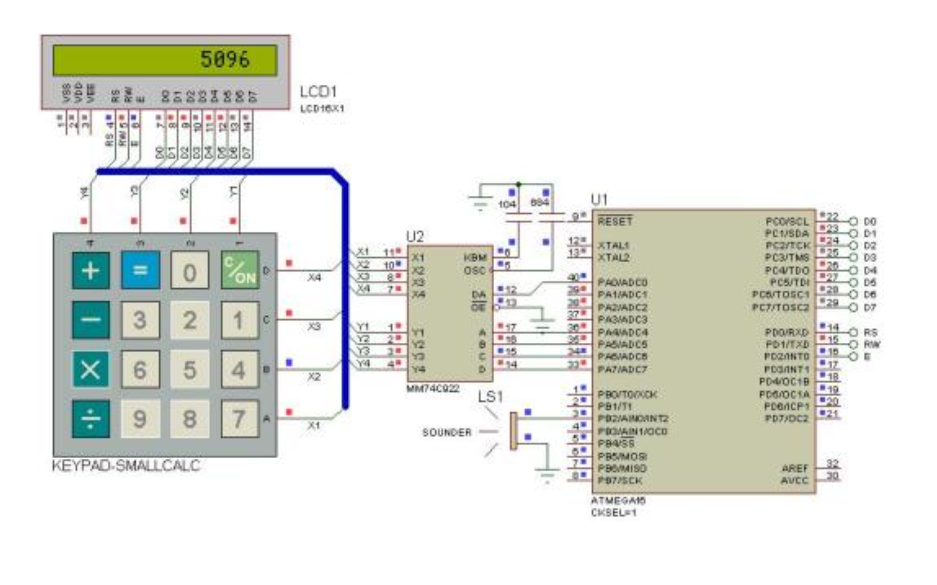

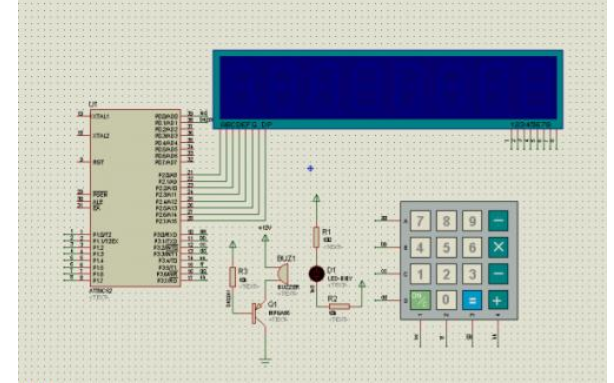

如何去实现基于单片机的四则运算计算器设计

使用51单片机设计一个四则运算带括号的计算器设计报告免费下载

使用51单片机实现简易四则运算计算器的资料和程序免费下载

基于单片机四则运算计算器设计+proteus仿真

FPGA中浮点四则运算的实现过程

FPGA中的浮点四则运算是什么

verilog整数四则运算的位宽考量简介

verilog整数四则运算的位宽考量简介

评论