中断操作三个步骤:

1、中断初始化

void intr_init(){//configure PLIC//cpu 0 accept all interrupts with priority above 0plic_set_threshold(BSP_PLIC, BSP_PLIC_CPU_0, 0);//enable SYSTEM_PLIC_USER_INTERRUPT_A_INTERRUPT rising edge interruptplic_set_enable(BSP_PLIC, BSP_PLIC_CPU_0, SYSTEM_PLIC_SYSTEM_AXI_A_INTERRUPT, 1);plic_set_priority(BSP_PLIC, SYSTEM_PLIC_SYSTEM_AXI_A_INTERRUPT, 1);//enable interrupts//Set the machine trap vector (../common/trap.S)csr_write(mtvec, trap_entry);//Enable external interruptscsr_set(mie, MIE_MEIE);csr_write(mstatus, MSTATUS_MPP | MSTATUS_MIE);}

其中包括设置中断门限。相应中断的使能,以及中断的优先级,数字越大,优先级越高。然后还有中断入中数据的保存。

2、trap处理

void trap(){int32_t mcause = csr_read(mcause);//Interrupt if true, exception if falseint32_t interrupt = mcause < 0;int32_t cause = mcause & 0xF;if(interrupt){switch(cause){case CAUSE_MACHINE_EXTERNAL: axiInterrupt(); break;default: crash(); break;}} else {crash();}}

3、用户中断处理

void axiInterrupt(){uint32_t claim;//While there is pending interruptswhile(claim = plic_claim(BSP_PLIC, BSP_PLIC_CPU_0)){switch(claim){case SYSTEM_PLIC_SYSTEM_AXI_A_INTERRUPT:bsp_print("Entered AXI Interrupt Routine, Passed!");break;default: crash(); break;}//unmask the claimed interruptplic_release(BSP_PLIC, BSP_PLIC_CPU_0, claim);}}

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

中断处理

+关注

关注

0文章

94浏览量

10967 -

RISC-V

+关注

关注

45文章

2271浏览量

46131

发布评论请先 登录

相关推荐

risc-v的mcu对RTOS兼容性如何

RISC-V的MCU对RTOS(实时操作系统)的兼容性主要取决于多个因素,包括RTOS的版本、RISC-V指令集的实现、以及芯片制造商提供的支持。以下是关于RISC-V的MCU对RTO

发表于 05-27 16:26

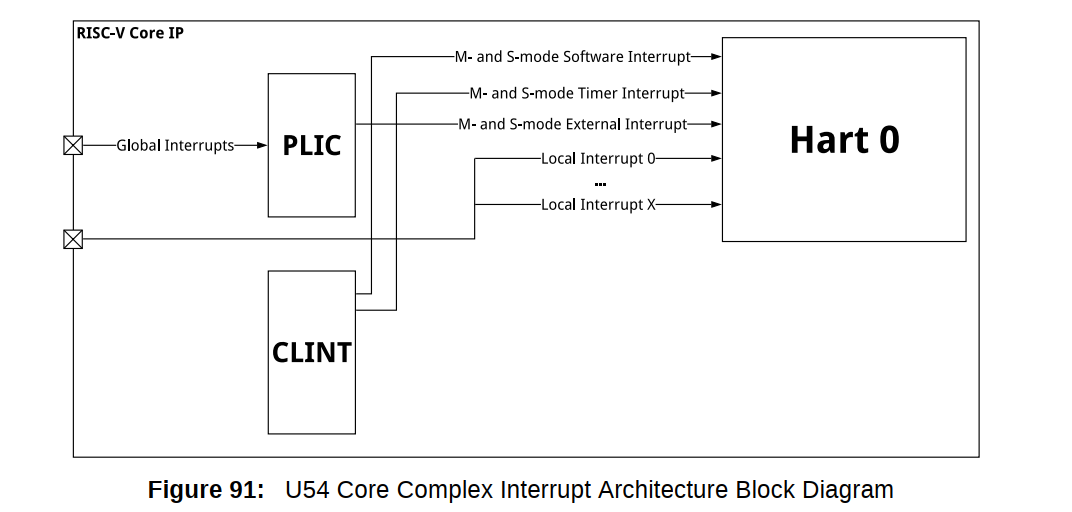

RISC-V架构及MRS开发环境回顾

—— CH32V103系列MCU。作为长久以来对RISC-V架构关注和研究的成果, RISC-V3A处理器,支持IMAC指令子集,内嵌了PFIC中断

发表于 12-16 23:08

如何在RISC-V处理器上使用FreeRTOS?

FreeRTOS内核调用哪个外部中断处理程序,设置外部中断handler的名称步骤如下:1 加载RISC-V芯片供应商提供的外部

发表于 11-29 15:54

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究

RISC-V架构的开源处理器与SoC。1 RISC-V简介1.1 RISC-V的基本设计RISC-V是一

发表于 07-27 18:09

FreeRTOS与RISC-V——适用于RISC-V的FreeRTOS概述

1.1简介FreeRTOS中面向RISC-V的接口是易于拓展的,其提供了一系列基本的接口,用于操作适用于所有RISC-V实现中的通用寄存器,以及一系列的宏来处理特定的硬件实现中涉及到的

发表于 04-09 09:26

RISC-V的异常处理机制复杂吗?

RISC-V对于异常处理的实现复杂吗?应该没有ARM Cortex系列的那样复杂,有NVIC或GIC中断控制器吧。那么它执行异常处理的流程是怎样的?

发表于 04-21 15:00

Sifive Learn Inventor基础之GPIO 按键中断 RISC-V

Sifive Learn Inventor 基础之gpio 按键中断Sifive Learn Inventor是Sifive的一款基于RISC-V内核的开发板,具体见官网的Hifive Rev b

发表于 12-20 19:06

•1次下载

MCU如何处理中断?中断处理过程包括哪些步骤?

当MCU接收到一个中断信号时,它会暂停当前正在执行的任务,保存现场,然后跳转到预设的中断处理程序(Interrupt Service Routine, ISR)去处理这个

RISC-V的中断处理 中断操作三个步骤

RISC-V的中断处理 中断操作三个步骤

评论