引 言

??在当今变化的市场环境中,产品是否便于现场升级,是否便于灵活使用成为产品能否进入市场的关键因素。在这种背景下,Altera公司的基于SRAM LUT结构的FPGA器件得到了广泛的应用。虽然这些器件应用广泛,但由于其内部采用SRAM工艺,它的配置数据存储在SRAM中。由于SRAM的易失性,每次系统上电时,必须重新配置数据,即ICR(In-Circuit Reconfigurability),只有在数据配置正确的情况下系统才能正常工作。在线配置方式一般有两类:一是通过下载电缆由计算机直接对其进行配置,二是通过配置芯片对其进行配置。通过PC机对FPGA进行在系统重配置,虽然在调试时非常方便,但在应用现场是很不现实的。上电后,自动加载配置对FPGA应用来说是必需的。Altera公司提供的配置芯片有一次可编程型和可擦除编程型两种:一次可编程型芯片只能写入一次,不适合开发阶段反复调试、修改及产品的方便升级;可擦除编程型价格昂贵,且容量有限,对容量较大的可编程逻辑器件,需要多片配置芯片组成菊花链形进行配置,增加系统设计的难度。

为了降低成本,目前在开发阶段多用可擦除型配置芯片;最终产品用不可擦写的配置芯片,但一次简单的代码更换就需要更换一次器件,这在产品升级时很不实用。至今还没有低成本的配置芯片出现,而我们采用的这套配置方案充分考虑了在FPGA实际使用中,对设计的保密性和设计的可升级的要求,不但可以实现代替价格昂贵的不可擦写和可擦写配置芯片,而且可以实现多任务电路结构重配置。该方案有PC机控制程序、单片机和外部串行存储器组成,只要通过替换外部串行存储器,就可实现对不同容量的多种配置芯片的代替。PC机是用来将配置数据写入存储器的,在写好数据后该配置系统不再需要PC机的控制,在单片机的控制下实现ICR或多任务电路结构重配置。多任务电路结构重配置即将多个配置文件分区存储到外部存储器中,然后由单片机接收不同的命令,以选择读取不同存储器区的数据下载到FPGA器件,实现在线配置成多种不同的工作模式。

1 FPGA器件的配置方式和配置文件

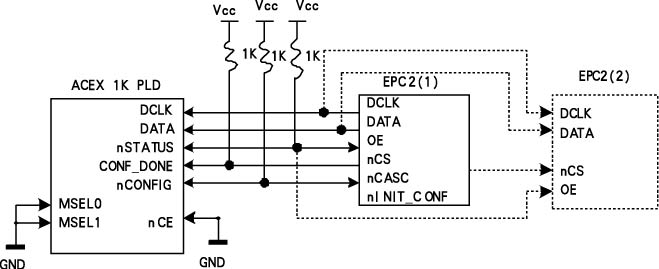

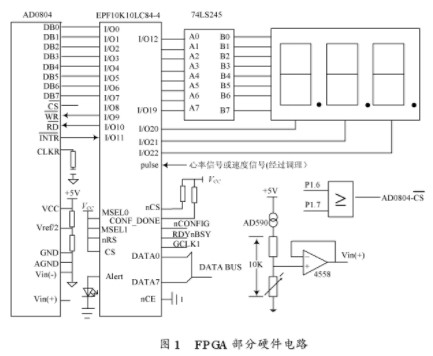

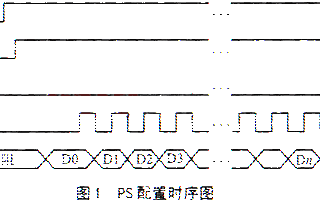

Altera公司生产的具有ICR功能的FPGA器件有FLEX6000、FLEX10K、APEX和ACEX等系列。它们的配置方式可分为PS(被动串行)、PPS(被动并行同步)、PPA(被动并行异步)、PSA(被动串行异步)和JTAG(Joint Test Action Group)等五种方式。这五种方式都能适用于单片机配置。PS方式因电路简单,对配置时钟的要求相对较低,而被广泛应用。我们的配置方案也采用PS配置方式来实现ICR功能,图1是PS配置方式的时序图。

被动串行工作过程:当nconfig产生下降沿脉冲时启动配置过程,在dclk上升沿,将数据移入目标芯片。在配置过程中,系统需要实时监测,一旦出现错误,nSTATUS将被拉低,系统识别到这个信号后,立即重新启动配置过程。配置数据全部正确地移入目标芯片内部后,CONF_DONE信号跳变为高,此后,DCLK必须提供几个周期的时钟(具体周期数与DCLK的频率有关),确保目标芯片被正确初始化,进入用户工作模式。

Altera的MAX+PLUS II或Quartus II开发工具可以生成多种配置或编译文件,用于不同配置方法的配置系统,而对于不同系列的目标器件配置数据的大小也不同,配置文件的大小一般有.rbf文件决定。.rbf文件即二进制文件。该文件包括所有的配置数据,一个字节的 .rbf文件有8位配置数据,每一字节在配置时最低位最先被装载。微处理器可以读取这个二进制文件,并把它装载到目标器件中。Altera提供的软件工具不自动生成 .rbf文件,须按照下面的步骤生成:① 在MAX+PLUS II编译状态,选择文件菜单的变换SRAM目标文件命令; ② 在变换SRAM目标文件对话框,指定要转换的文件并且选择输出文件格式为 .rbf(Sequential),然后确定。

2 配置电路结构和原理

2.1 串行通信的电路结构和原理

PC机与单片机的接口如图2所示。AT89C2051单片机通过串行口直接接收PC机传送来的串行数据,然后把接收到的数据存入数据存储器。由于PC机的串行口都是RS-232C标准的接口,所以,其输入输出在电平上和采用TTL电平的AT89C2051在接口时会产生电平不同的问题。为了解决这个问题,在PC机和单片机的串行通信电路中加入了MAX232芯片,以实现TTL电平和RS-232C接口电平之间的转换。这样PC机和AT89C2051单片机进行串行通信时就可以顺利进行了。除了电路结构之外,要实现PC机和AT89C2051之间的通信,还需要有合适的通信软件。

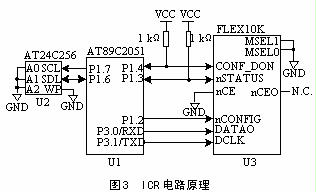

2.2 ICR控制电路原理

ICR电路原理如图3所示。AT24C256用来存储FPGA的配置数据。

ICR控制电路的工作过程为:经MAXPLUS II编译生产的配置文件(.sof)通过格式转换成为 (.rbf)。然后,利用PC机端的控制程序,通过PC机的串行通信口,经U1存储在U2中。U1再根据系统的要求,通过P1.2、P1.3、P1.4、P3.0和P3.1等5个I/O口,将其存储在U2中的配置数据下载到电路中的FPGA器件中去。

因作者设计电路中的FPGA是Altera公司的FLEX系列的EPF10K10,其配置文件的容量为15KB,故电路中采用1片AT24C128就可存储EPF10K10的配置数据。我们选用AT24C256器件可以存储两个配置文件,是为了实现多任务电路重构,此时整个ICR控制电路只有2片IC。可以说,它是目前结构最简单、成本最低的ICR控制电路。如果配置的FPGA是EPF10K30或更大门数的器件,则需要大容量的存储器件或多片AT24C256。(在两线串行总线上最多可接4片AT24C256。)

3 软件设计

在该配置方案中,软件包括在PC机端的控制软件和在AT89C2051端的控制软件两部分。PC机端的软件采用Visual Basic语言编程,而AT89C2051采用汇编语言进行编程。

3.1 PC机端的软件

PC机端的软件采用Visual Basic语言编程。VB支持面向对象的程序设计,具有结构化的事件驱动编程模式,而且可以十分简便地作出良好的人机界面。PC机端的控制程序主要实现读取.rbf文件并将其通过串口送出的功能。读取文件时,主要使用读取二进制文件命令。在串口通信方面,使用VB提供的具有强大功能的串口通信控件MSCOMM。该控件可设置串口状态及串口通信的信息格式和协议。

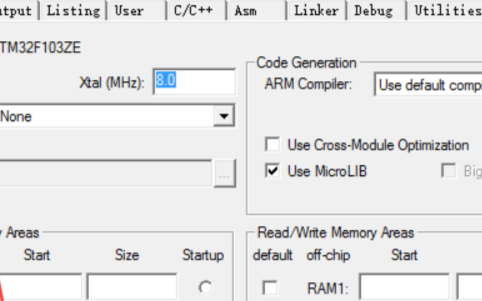

在实际工作中,要实现AT89C2051和PC机之间的有效通信,必须使其具有相同的波特率和相同的通信协议。作者采用了9600bps的波特率和N.8.1帧结构。N.8.1帧结构表示1帧串行数据有10位:起始位占用1位(低电平),用来表示字符开始;后8位为数据编码,无奇偶校验位;最后为停止位(高电平),用来表示字符传送结束。单片机的串行口工作在方式1。方式1是标准的10位异步通信方式,10位数据和PC机的标准串口相对应,传送的波特率由单片机工作时钟和T1的溢出率共同决定。

3.2 ICR控制电路软件

在图3介绍的ICR控制电路中,其存储FPGA配置数据的存储器 AT24C256采用I2C串行总线进行数据交换。其数据交换速度较慢,而FPGA配置数据又比较大,因此如何提高图3介绍的ICR控制电路的配置速度将是软件设计上的一个重点。限制速度的瓶颈主要是从AT24C256读取数据和将数据写入FPGA器件中。从AT24C256读取数据,有读当前地址、随机读和顺序读三种方式。这三种方式中,顺序读最简单、速度最快。因为在同一片AT24C256中,仅需要写入一次读命令就可以按顺序从0地址开始直至读完整片AT24C256中的全部数据。向FPGA器件写数据时,可以使用串行口的移位寄存器工作方式,即方式0。方式0数据的传送以8位为1帧,无论是发送或是接收都是最低有效位居先。这和FPGA对数据的要求一致,传送的波特率固定为振荡频率的1/12。本系统只需用到输出方式,串行数据通过RXD端输出,而用TXD端输出移位脉冲。当1字节数据写入串行数据缓冲器SBUF时,就开始发送。在此期间,发送控制器送出移位信号,使发送移位寄存器的内容右移1位,直至最高位(D7位)移出后,停止发送数据和移位时钟脉冲。发送完1字节数据后,硬件置发送标志位TI为1,通过判断TI的状态决定是否向SBUF写入数据。采用这种方式比采用普通(I/O)口要快很多。

4 结 论

我们设计的基于微控制器的FPGA器件的 ICR控制系统,具有线路结构简单、开发容易、体积小、成本低的优点;可以支持3.3V和5V系统的配置;适用于需要ICR功能的电子装置中。该ICR控制电路是为配置Altera公司FLEX系列的FPGA器件而设计的,稍加修改也适用于其它系列的FPGA器件。这个配置电路的主要弱点在于配置速率较慢,只能适用于配置速率要求不高的应用。

王玉化:工程师,研究方向EDA威廉希尔官方网站

和嵌入式可编程系统。

- 配置方法(7747)

- 组图FP(5547)

相关推荐

FPGA芯片配置方式及常见配置方法

9490

9490FPGA可重复配置和测试系统的实现

1414

1414

远程在线更新FPGA程序的方法

27516

27516

基于SPI FLASH的FPGA多重配置

13669

13669

FPGA 是如何分类的?FPGA的使用方法

FPGA在线配置

FPGA在线配置模块和自动测试模块实现过程

FPGA配置电路

FPGA配置问题

FPGA中SPI复用配置的编程方法

FPGA实战演练逻辑篇13:配置电路

FPGA实战演练逻辑篇69:基于FPGA的在线系统调试概述

FPGA的接口配置如何进行配置?

FPGA芯片_GW2AN-55器件原理图指导手册

fpga 多配置的问题

Altium designer高版本如何在线搜索元器件

STM32单片机是怎样配置FPGA的

Xilinx FPGA在线更新配置数据交流

Xilinx FPGA入门连载17:PWM蜂鸣器驱动之复位与FPGA重配置功能

一种基于DSP和JTAG接口的FPGA系统在线编程设计

使用高速SPI Nor Flash的FPGA配置

例说FPGA连载13:灵活定制——配置电路

例说FPGA连载18:配置电路设计

几组实用FPGA原理设计图

勇敢的芯伴你玩转Altera FPGA连载14:FPGA下载配置电路

勇敢的芯伴你玩转Altera FPGA连载52:Altera FPGA配置方式之AS/PS/JTAG配置方式

勇敢的芯伴你玩转Altera FPGA连载53:PWM蜂鸣器驱动之FPGA在线下载配置

如何使用高速NOR闪存配置FPGA

支持重构的FPGA器件

有什么FPGA可重构方法可以对EPCS在线编程?

有什么好的FPGA在线培训班吗?

玩转Zynq连载5——基于Vivado的在线板级调试概述

电源组用的元器件

谈谈Altera FPGA的配置

可在线升级的FPGA并行配置方法的实现

23

23FPGA器件在嵌入式系统中的配置方式的探讨

10

10DSP和FPGA共用FLASH进行配置的方法

12

12基于单片机的Cyclone系列FPGA配置方法

64

64FPGA的全局动态可重配置威廉希尔官方网站

54

54FPGA器件的在线配置方法

448

448ACEX 1K系列CPLD配置方法探讨

478

478

FPGA器件的在线配置方法

1062

1062

FPGA 重复配置和测试的实现

528

528

基于对EPCS在线编程的FPGA可重构方法

1310

1310FPGA中SPI复用配置的编程方法

3061

3061

FPGA重复配置和测试的实现

544

544

基于JTAG接口实现ARM的FPGA在线配置设计

3141

3141

ARM设计的FPGA可重构配置方法的实现及应用

1326

1326

使用CPLD和Flash实现FPGA的配置

8194

8194

一种基于SRAM的FPGA的加密方法

48

48Leon3的接口配置设计

1474

1474

Leon3软核的FPGA SelectMap接口配置设计

3151

3151

微处理器系统中连接简单的被动串行配置方法和被动并行异步配置方法

1

1V5 FPGA配置回读

8730

8730反熔丝FPGA配置和编程方法

10165

10165

FPGA配置与测试的详细方法分析与特点

5921

5921

关于fpga编程flash芯片和配置数据技巧

24007

24007

AS配置方式由FPGA器件引导配置操作过程

11628

11628

FPGA的配置/加载方式

17251

17251基于ICR威廉希尔官方网站 的FPGA配置电路硬件设计及其工作原理

4908

4908

FPGA配置相关笔记

481

481FPGA教程之CPLD和FPGA的配置与下载的详细资料说明

17

17以Flash控制器为核心的FPGA在线更新功能实现设计流程介绍

2746

2746

Spartan-6 FPGA的配置教程说明

25

25FPGA的三种配置方式详解

7500

7500基于FPGA器件EP20K200E芯片的配置方式在嵌入式系统中的应用研究

878

878

FPGA有哪些主要配置方式?

11307

11307

FPGA_ASIC-DSP和FPGA共用FLASH进行配置的方法

21

21FPGA芯片配置分类及配置方式

6052

6052FPGA CPLD可编程逻辑器件的在系统配置方法

13

13在配置FPGA器件时的常见问题及其解决方法

1140

1140FPGA配置模式和配置设计

862

862FPGA在线调试的方法简单总结

1225

1225

使用高速NOR闪存配置FPGA

331

331

电子发烧友App

电子发烧友App

评论