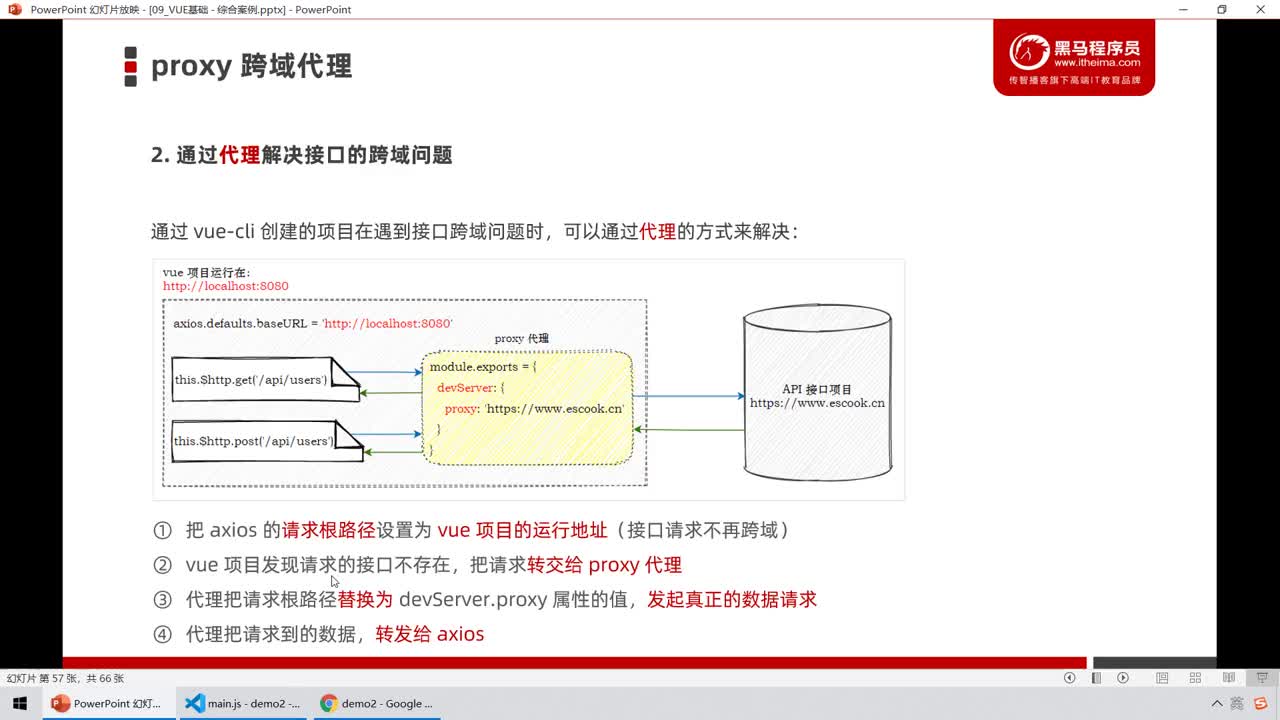

前后端分离开发中必要会遇到的问题—跨域。在使用vue开发的时候,开始为了解决跨域问题。采用的是CORS(Cross-origin resource sharing)。后台在响应头中添加Access-Control-Allow-Origin。这样就可以跨域调后台接口了。

在前几天无意中看到了config的index.js文件中有一个proxyTable属性,通过配置可以解决开发环境的跨域

开发期间的API代理

当将此样板与现有后端集成时,通常需要在使用dev服务器时访问后端API。为了实现这一点,我们可以并行(或远程)运行dev服务器和API后端,并让dev服务器将所有API请求代理到实际的后端。

要配置代理规则,请在其中编辑dev.proxyTable选项config/index.js。dev服务器正在使用http代理中间件进行代理,因此您应参考其文档以获取详细的用法。但这是一个简单的例子:

// config/index.js

module.exports = {

// ...

dev: {

proxyTable: {

// proxy all requests starting with /api to jsonplaceholder

‘/api’: {

target: ‘http://jsonplaceholder.typicode.com’,

changeOrigin: true,

pathRewrite: { //需要rewrite重写的, 如果在服务器端做了处理则可以不要这段

‘^/api’: ‘’

}

}

}

}

}

上面的示例将代理请求/api/posts/1到http://jsonplaceholder.typicode.com/posts/1。

如果 pathRewrite: {

‘^/api’: ‘api’

},

则将代理请求/api/posts/1到http://jsonplaceholder.typicode.com/api/posts/1。

网址匹配

除了静态网址之外,您还可以使用glob模式来匹配URL,例如/api/**。有关详细信息,请参阅上下文匹配。此外,您可以提供一个filter可以是自定义函数的选项,以确定请求是否应被代理:

proxyTable: {

‘*’: {

target: ‘http://jsonplaceholder.typicode.com’,

filter: function (pathname, req) {

return pathname.match(‘^/api’) && req.method === ‘GET’

}

}

}

电子发烧友App

电子发烧友App

评论