AMD XILINX 近期全新推出了 Vivado ML Editions 2022.2 版给工具集带来了多项重大改进与增强功能。

主要亮点

推出电源设计管理器:

电源设计管理器 (PDM) 是全新的下一代功耗评估平台,设计目的是为 Versal 和 Kria SOM 提供准确一致的功耗估计能力。电源设计管理器是 Versal Prime、Premium、AI Core 和 AI Edge 系列等 Versal 产品家族的首选功耗评估工具。

PDM 为 Versal ACAP 硬 IP 块提供增强向导,简化从 XPE 向 PDM 的迁移,帮助用户获得准确的功耗评估。

面向 Versal 器件和 UltraScale+ 器件

的智能设计运行 (IDR) 增强功能

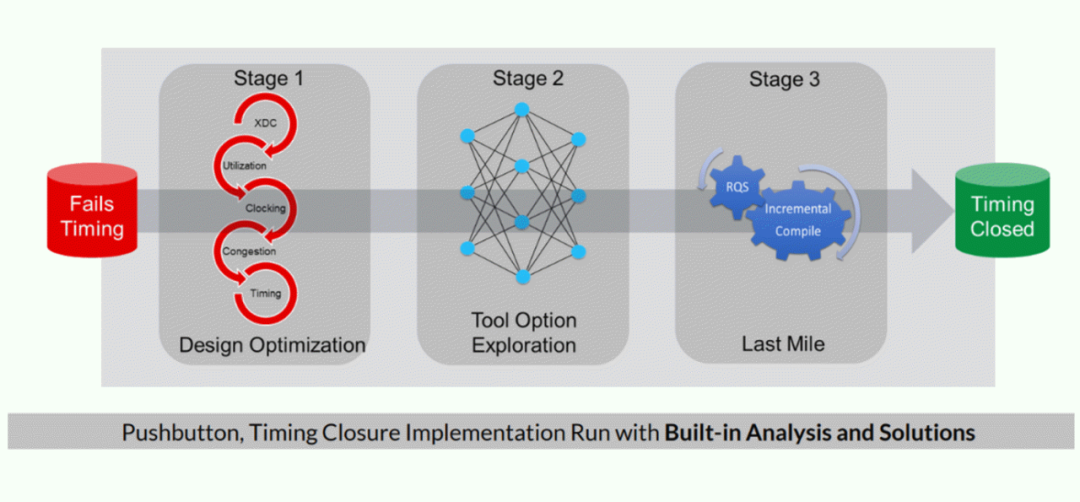

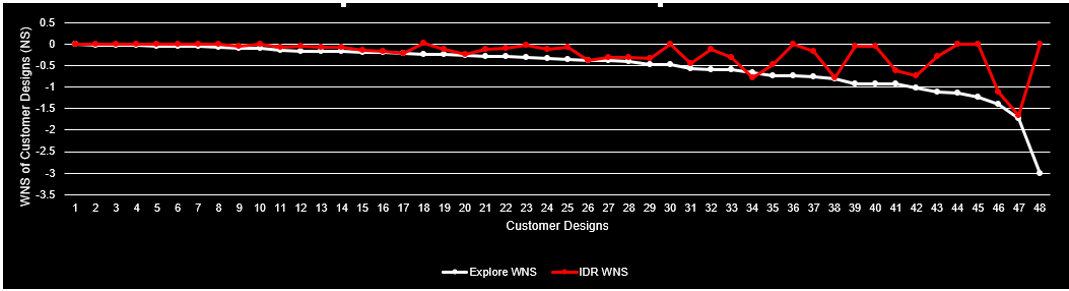

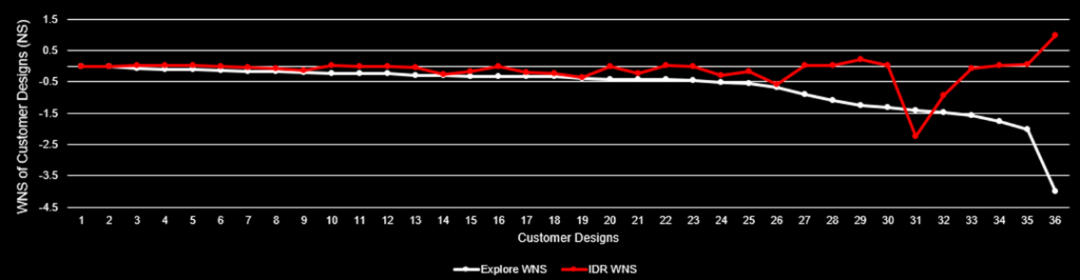

智能设计运行 (IDR) 是基本无需用户干预的一键式时序收敛流程。在 2022.2 版中,我们首次为 Versal 器件提供 IDR 增强功能。使用 IDR 后,我们看到 Versal ACAP 设计的 QoR 平均提高 5%,UltraScale+ 器件设计的 QoR 平均提高 10%。下面是用 Explore 策略运行设计和用 IDR 流程运行设计的比较。为了比较 QoR,我们测量了一系列设计中的最差建立时间时序裕量 (WNS)。WNS 是一个衡量最差建立时间时序裕量的指标,其满足建立时间的值是大于等于0 纳秒。

上图所示的是用 Explore 策略和用智能设计运行 (IDR) 在 48 个 Versal ACAP 客户设计上获得的基准测试结果。在这 48 个设计中,IDR 实现了对 WNS 平均 5% 的改进。

此外,还对指向 UltraScale+ 器件的一系列设计运行了 IDR。下图所示的是用 Explore 策略和用智能设计运行 (IDR) 在 36 个客户设计上获得的基准测试结果。在这些设计中,IDR 实现了对 WNS 平均 10% 的改进。

增量实现强化

Vivado IDE 中的增量实现流程允许用户在后续的实现过程中直接使用以前工程的相同设计部分的实现结果,从而节省运行时间,提高运行结果的可预测性。

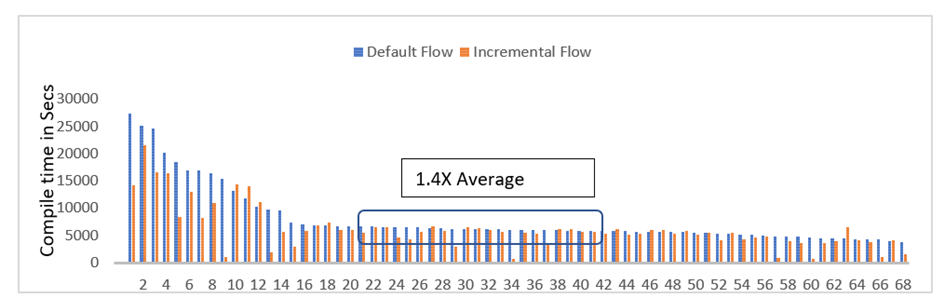

在 2022.2 版中,UltraScale+ 器件设计的编译速度比默认流程快 1.4 倍。现在也对 Versal 单片器件提供增量实现功能。

根据在 68 个 UltraScale+ 客户设计中使用默认流程和使用增量流程得到的基准测试结果,增量流程的编译速度加快了 1.4 倍。

Dynamic Function eXchange (DFX) 强化

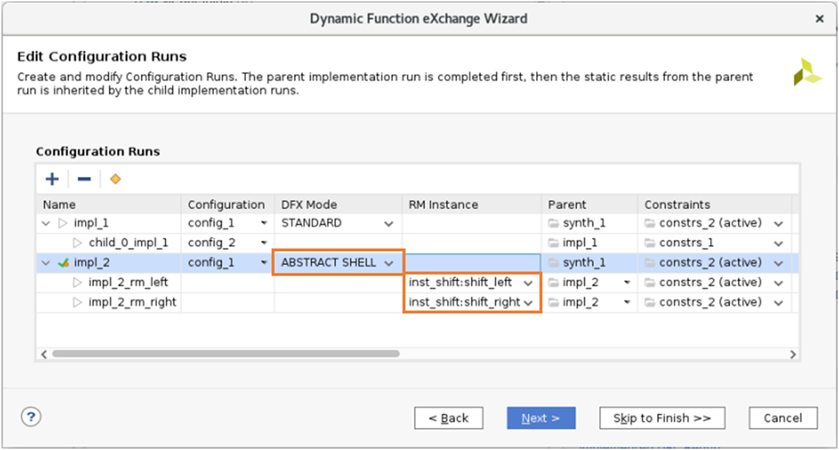

抽象 Shell 是一项帮助所有可重配子模块运行缩短编译时间的功能。2022.2 版允许抽象 Shell 支持 Versal 器件。

抽象 Shell 现在提供基于工程模式的支持。在基于工程模式支持下,该工具可自动管理用户的设计流程和设计数据。使用基于工程的支持模式,Vivado IDE 跟踪设计历程,存储相关的设计信息。

此外,Dynamic Function eXchange 现在支持 Versal Premium SSI 器件。

Dynamic Function eXchange 具有通过下载部分比特文件动态修改可重配逻辑子模块,而其余逻辑将继续不间断运行的功能。

审核编辑 :李倩

-

amd

+关注

关注

25文章

5251浏览量

132812 -

电源设计

+关注

关注

30文章

1506浏览量

65551 -

Xilinx

+关注

关注

70文章

2129浏览量

119594

原文标题:Vivado® ML Editions 2022.2 最新更新

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AMD推出全新Spartan UltraScale+ FPGA系列

使用 PCIE 更新 AMD ZYNQ™ 的 QSPI Flash 参考设计

AMD Vivado Design Suite 2023.2的优势

罗彻斯特电子携手AMD/Xilinx可持续供应Xilinx传统FPGA产品

AMD推出全新AMD EPYC(霄龙)8004系列处理器

Vivado ML版中动态函数交换的威廉希尔官方网站 进步

【KV260视觉入门套件试用体验】+02.开发环境安装Vitis/Vivado(zmj)

如何实现基于FPGA Vivado的74系列IP封装呢?

AMD XILINX全新推出了Vivado ML Editions 2022.2版

AMD XILINX全新推出了Vivado ML Editions 2022.2版

评论