由于项目需要,小编使用Aurora核对数据进行光纤传输,这篇文章主要介绍如何生成Aurora核、仿真上板测试。

一、Aurora IP建立

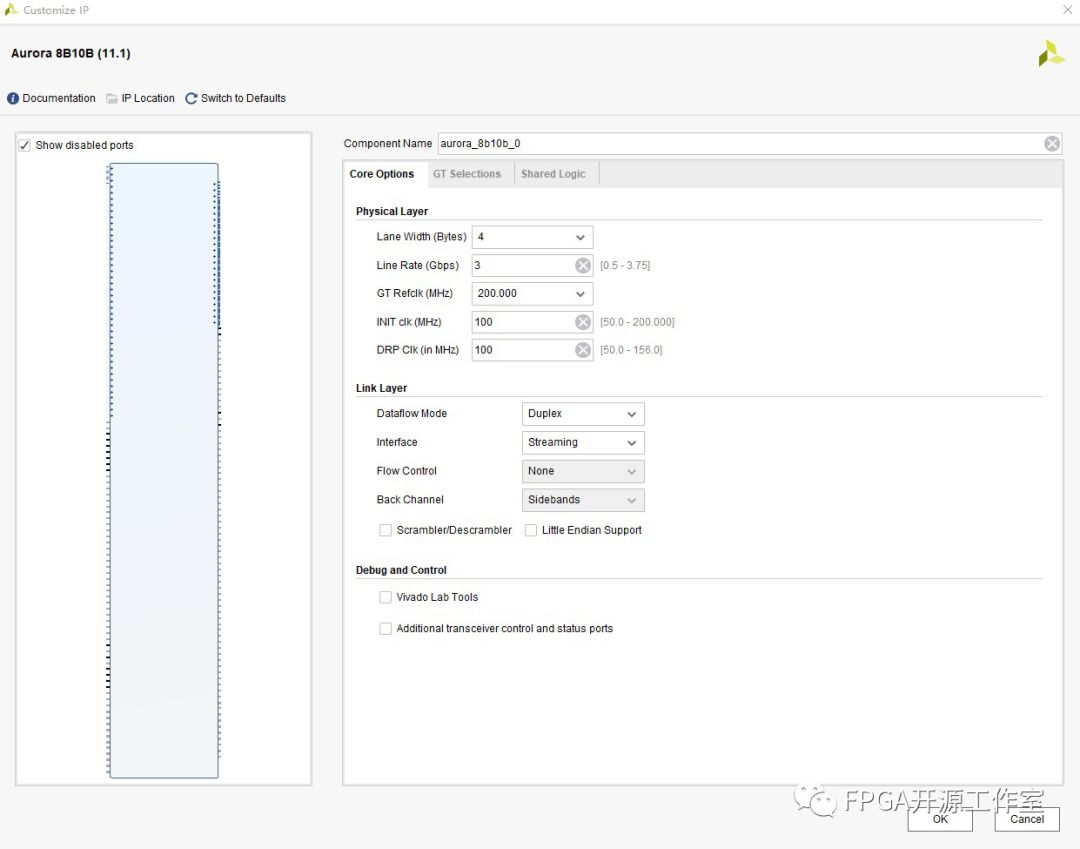

第一步

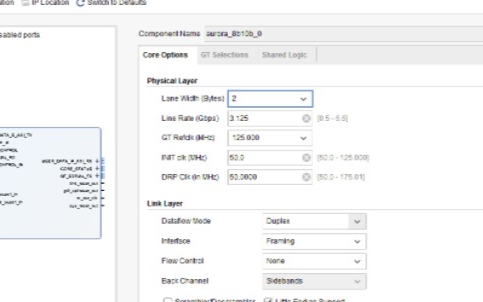

1》lane Width:用户数据接口 4(32bit) 2(16bit)

2》Line Rate:3Gbps 假设图像数据为1280x1024 @60 RGB(24bit),那么 1280 pixels/row x 1024 rows x 8bits/element gray scale x 3 elements/pixel x60 Hz refresh x 1.25 8b/10b x 1.05 (typical FC-AV protocol overhead) is approximately equal to 2.5 Gbps.

3》GT Refclk:200(此处查看板子原理图即可)

4》INIT clk:100MHz

5》DRP clk:100MHz

上述两个时钟在参考范围内设置相同即可,本页其他选项如图设置即可 。

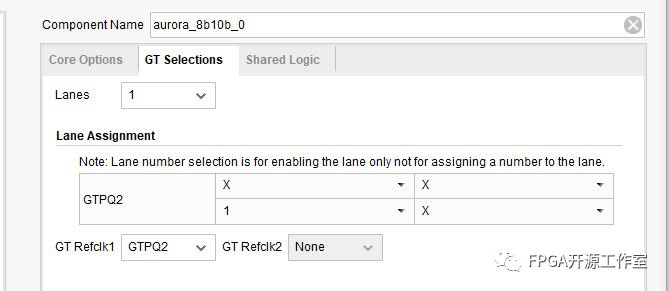

第二步

选择高速串行通道的位置,默认即可 。

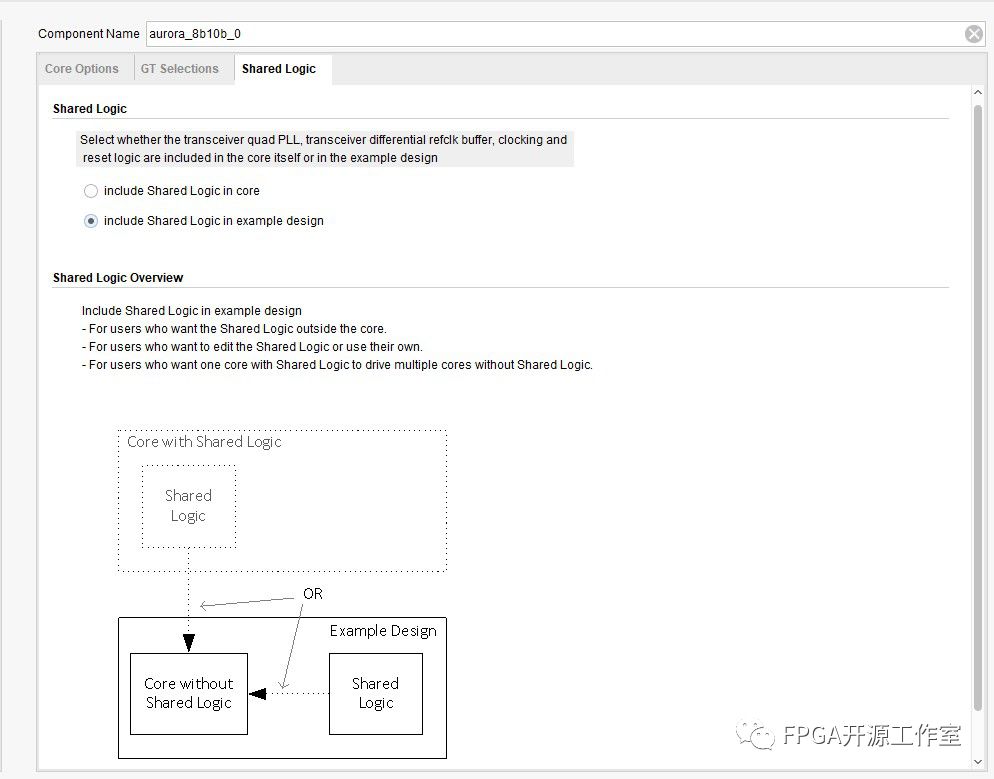

第三步

默认即可。

二、仿真测试

在Vivado软件中,我们生成好IP后可以可以打开带有例子的工程,进行仿真查看LANE_UP和CHANNEL_UP信号拉高后,即可认为光纤通道初始化成功,在对其数据接口进行查看,官方给的例程主要分为三大块,数据产生模块、光纤传输模块、数据检查模块 。

三、上板测试(光纤初始化)

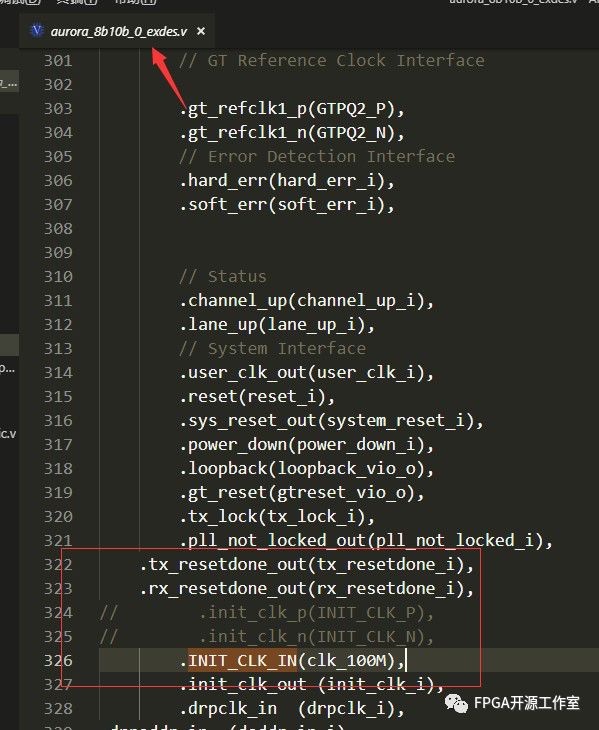

我们需要对INIT_CLK_P、INIT_CLK_N、DRP_CLK、GT_RESET_IN、RESET四个信号进行修改。

第一步

INIT_CLK_P、INIT_CLK_N:我们利用板子的单端输入时钟27M进行pll倍频出的100M提供给INIT_CLK_IN。

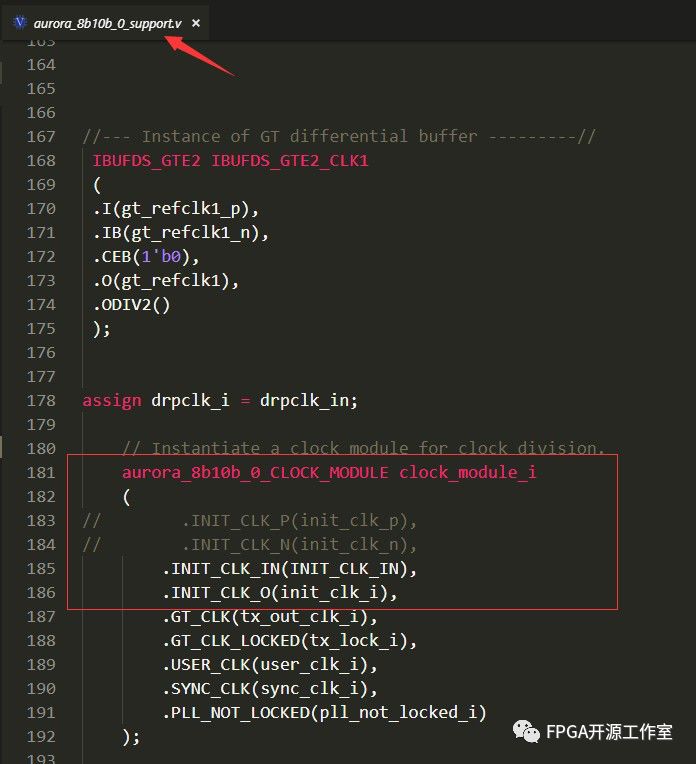

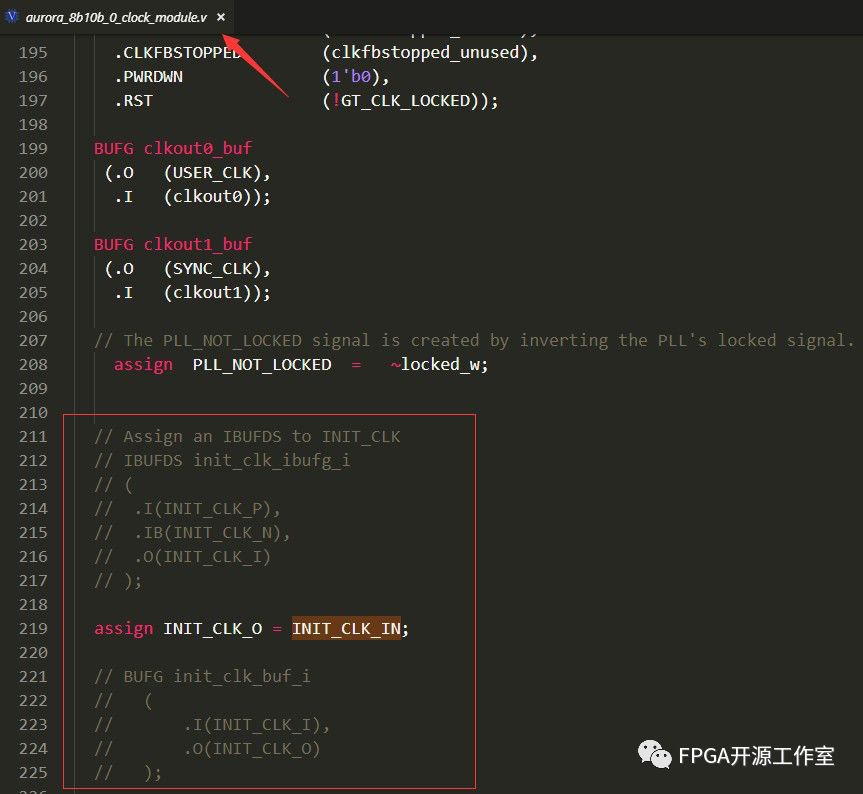

将aurora_8b10b_0_exdes文件做如下修改

将aurora_8b10b_0_support文件做如下修改

将aurora_8b10b_0_CLOCK_MODULE文件做如下修改

第二步

DRP_CLK:将倍频出的100M时钟输入给DRP_CLK即可。

第三步

GT_RESET_IN、RESET:如果板子上有硬复位(低有效),对其取反赋给其即可,在顶层aurora_8b10b_0_exdes中修改。

assign RESET = ~sys_rst_n;

assign GT_RESET_IN = ~sys_rst_n;

第四步

如果我们板子上有指示灯,我们可以通过指示灯来查看是否初始化成功。在顶层aurora_8b10b_0_exdes中修改。

assign CHANNEL_UP_led = ~CHANNEL_UP;

assign LANE_UP_led = ~LANE_UP;

我们的指示灯是低电平亮,所以对其取反,上板烧写例程代码后可以看到两个指示灯点亮,我们就可以认为此时光纤核初始化成功。

学会使用Aurora核之后,那么我们就需要利用相关协议进行传输,小编在本次项目中使用ARINC818协议

对数据进行封装,然后过光纤进行传输,最后回传到sdi芯片进行显示,开发者可根据项目需要选择协议对数据进行传输。

审核编辑 :李倩

-

仿真

+关注

关注

49文章

3835浏览量

131695 -

光纤通道

+关注

关注

0文章

220浏览量

13989

发布评论请先 登录

相关推荐

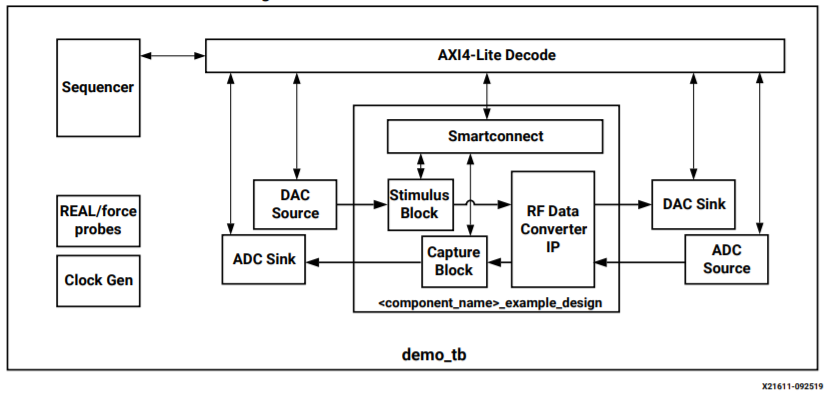

RF Data Converter IP设计仿真测试激励文件原理

Aurora 8b/10b IP核问题

GTY 100G Aurora IP的一些问题

Aurora IP 8b10b如何生成bitfile?

用于26Km光缆的Aurora IP v11.0通道上行/上行故障的解决办法?

如何使用Aurora 8B / 10B建立仅传输?

怎么禁用Aurora IP Core 8B / 10B中的时钟补偿功能?

40Gbs交换IP软核验证和测试

Aurora OS是个什么来头?

IP仿真的实体或块级别是如何完成的

测试与验证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真

基于FPGA的Aurora 8b10b光通信测试方案

Aurora IP建立仿真及测试

Aurora IP建立仿真及测试

评论