一、Xilinx(全球FPGA市场份额最大的公司,其发展动态往往也代表着整个FPGA行业的动态) (....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-18 11:48

•2055次阅读

1、符号能量问题 请问各位大虾,像4QAM,16QAM,32QAM,64QAM调制每符号平均能量怎么....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-18 11:35

•6249次阅读

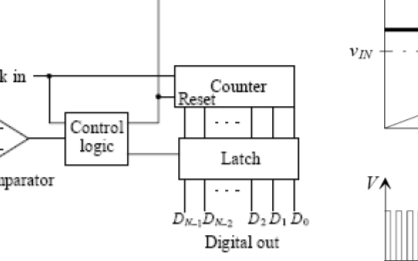

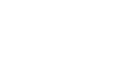

本文来梳理ADC两个方面的内容,常见的ADC类型及原理,以及可能容易掉进去的坑。 谈谈我为什么整理这....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-18 11:31

•11355次阅读

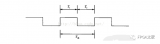

一、时钟相关概念 理想的时钟模型是一个占空比为50%且周期固定的方波。Tclk为一个时钟周期,T1为....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-15 09:37

•4568次阅读

1.项目需求 FPGA :V7-690T两片 Resource:两片FPGA通过X12 gth互联;....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-07 10:15

•4770次阅读

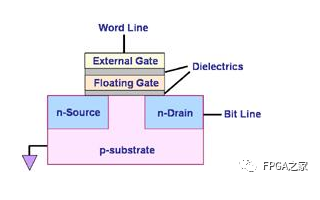

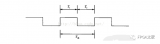

概述 Flash名称的由来,Flash的擦除操作是以block块为单位的,与此相对应的是其他很多存储....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-07 10:12

•6958次阅读

卡尔曼滤波实质上就是基于观测值以及估计值二者的数据对真实值进行估计的过程。预测步骤如图1所示: 图1....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-07 10:08

•9662次阅读

作为一名电子人,咱们都知道随着摩尔定律的提出,为半导体产业指明了之后几十年的发展之路。然而许多人不知....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 01-07 10:04

•1705次阅读

本文通过阅读内核代码,来梳理一下I2C子系统的整体视图。在开发I2C设备驱动程序时,往往缺乏对于系统....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-31 10:40

•1988次阅读

调制的概念 调制(modulation)就是对信号源的信息进行处理加到载波上,使其变为适合于信道传输....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-31 10:37

•7577次阅读

刚参加工作那会,没想过去读源码,更没想过去改框架的源码;总想着别人的框架应该是完美的、万能的,应该不....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-31 10:29

•1471次阅读

在大数据和人工智能盛行的今天,金融科技(Fintech)领域数据日益密集和敏感,在高频交易、风险分析....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-28 09:50

•2174次阅读

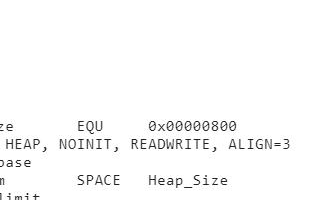

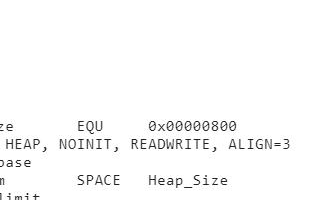

在嵌入式裸机编程中,作为一名初级的CODER。经常要与CPU、内存等打交道。CPU作为系统的动力....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-28 09:44

•2724次阅读

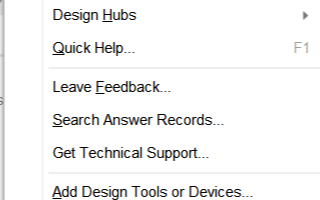

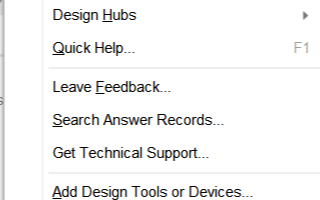

有的时候需要查找一些官网的例程进行学习和参考,但是总感觉无从下手,今天就教大家怎么利用官网和Viva....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-28 09:39

•2151次阅读

这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 12-26 10:20

•2535次阅读

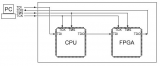

JTAG可以控制(or hijack)所有IC的引脚。在图片上,也许JTAG将使所有CPU引脚输出,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-29 11:21

•2358次阅读

在工业领域应用最多的应该是485 232的电平标准,两者各有优缺点,成本低,使用也比较简单,但是依然....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-29 11:17

•4248次阅读

通用异步收发传输器(Universal Asynchronous Receiver/Transmit....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-29 11:12

•2459次阅读

单粒子翻转(Single-Event Upsets,SEU)指的是元器件受辐照影响引起电位状态的跳变....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-29 11:07

•5242次阅读

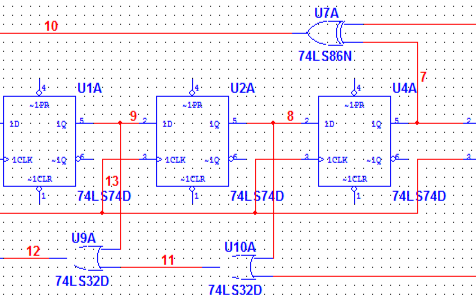

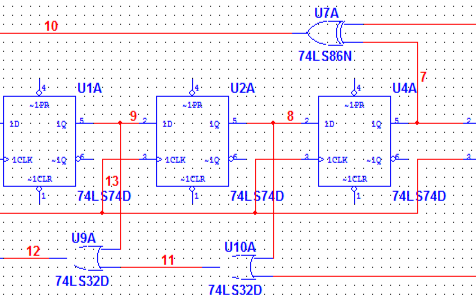

这里带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-29 11:04

•3969次阅读

线程是CPU调度的最小单位(程序执行流的最小单元),它被包含在进程之中,是进程中的实际运作单元。一条....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-29 11:01

•13000次阅读

要求一个同时具备设计面积最小、运行频率最高是不现实的。更科学的设计目标应该是在满足设计时序要求(包括....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-29 10:58

•1736次阅读

作为一名程序员,与计算机打交道的日子不计其数,不管你玩硬件还是做软件,你的世界自然都少不了计算机最核....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-05 18:10

•4093次阅读

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-02 11:27

•3994次阅读

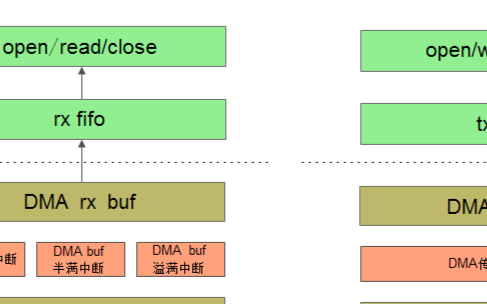

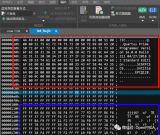

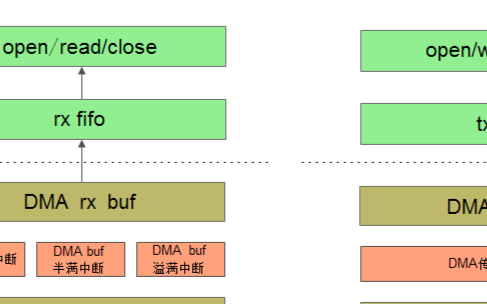

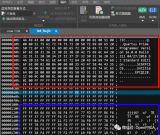

偶然看到一篇很干文章,整理分享给大家: 1 前言 直接存储器访问(Direct Memory Acc....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-02 11:24

•3230次阅读

CPU的本体芯片被牢固安装在封装的中心。称不上巧合的是CPU芯片的形状同样为矩形,所以我们就先来讲一....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 11-01 11:24

•1728次阅读

打开后的界面如下图所示,全英文显示。如果感觉自己的英文水平欠佳,可以使用谷歌浏览器打开该网页,并选择....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-23 10:33

•4863次阅读

在做在线远程升级的时候,一般需要两步:1、将数据写到外挂的flash中。2重新启动FPGA配置。 不....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-23 10:24

•1480次阅读

据《华尔街日报》最新报道,超微半导体(AMD)正就收购芯片制造商赛灵思(Xilinx)展开深入谈判,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-23 10:16

•1762次阅读

本文是一篇详细介绍ISSCC2020会议上一篇有关亚稳态解决方案的文章,该威廉希尔官方网站

也使得FPGA在较高频....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-22 18:00

•3831次阅读