百度百科对UVM的释义如下:通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

2022-11-30 12:47:00 431

431 后面有专门的人员进行布局布线,而且是专用的布局布线软件工具。 不同点 可编程性:FPGA可重构电路,完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写;ASIC永久电路,ASIC需要较长的开发周期,风险较大,一旦有问题,成片全部作废。 功耗:在相同工艺条件下,

2022-11-28 10:30:13 266

266 Knowledge of SoC (ASIC/FPGA) design and verification tools. System One to Two

2009-04-10 15:17:03

利用Systemverilog+UVM搭建soc验证环境

2022-08-08 14:35:05 1

1 ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)今日发布FPGA-Go-ASIC验证平台。

2022-07-29 10:08:16 446

446 什么是FPGA原型? FPGA原型设计是一种成熟的威廉希尔官方网站

,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和

2022-07-19 16:27:29 994

994 需要门级验证:FPGA 和 ASIC 一样需要设计级验证。但是,FPGA 在门级不是细粒度的,因此它们不需要门级验证。您将每个门都放置在 ASIC 设计中,因此您需要验证每个门。

2022-06-20 16:13:05 1795

1795

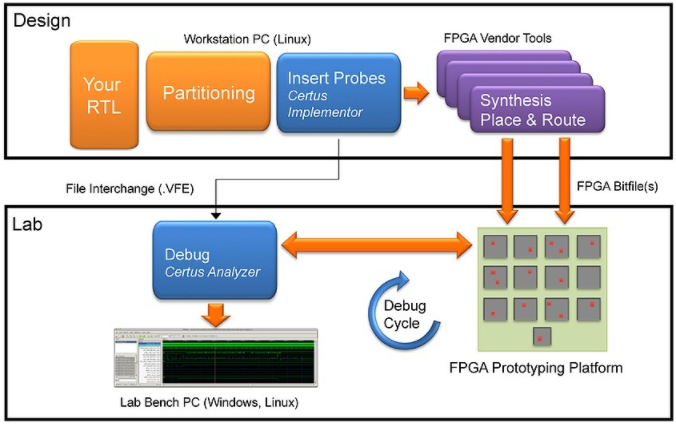

随着复杂性的增加和对探测点的访问受限,ASIC 和 FPGA 验证和调试变得乏味且耗时。随着越来越多的功能集成到每个芯片中,对探测点的物理访问变得不可能。

2022-06-19 07:40:00 482

482

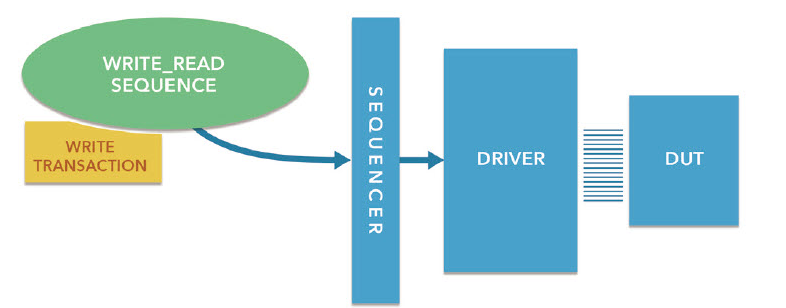

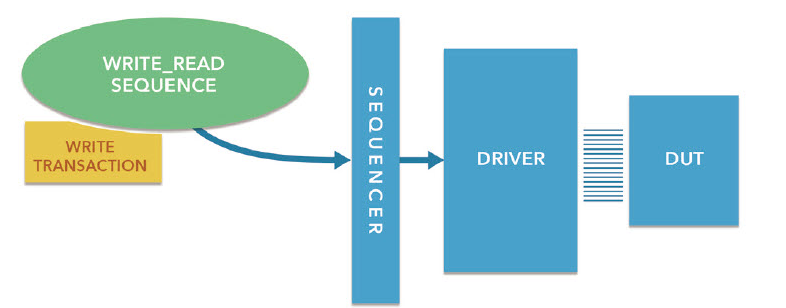

直观的印象,就是uvm验证平台,它是分层的结构。图中的每一个巨型框都代表着平台的一个构成元素。这些元素呢,我们称为平台组建,下面来简单的分析一下。从最底层上来看,agent 中包含了driver,monitor和sequencer,其中driver ,monitor中也包含了与dut进行

2021-12-09 13:36:13 7

7 SystemVerilog通用验证方法(UVM)是一种生成测试和检查结果以进行功能验证的有效方法,最适合用于块级IC或FPGA或其他“小型”系统。在UVM测试台中,大多数活动是通过编写序列来生

2021-04-09 16:09:11 2585

2585

本文是本人对xilinx XC7V系列FPGA用于ASIC前端验证遇到问题的总结,为自己记录并分享给大家,如果有歧义或错误请大家在评论里指出。

2021-01-12 17:31:44 9

9 Express 5.0的物理层和电气接口。 新思科技CXL验证IP基于新一代SystemVerilog的 Universal Verification Methodology(UVM)架构,使验证IP的集成

2020-12-26 11:04:10 2080

2080 本周美国海关及边境保卫局宣布将在更多机场中实行“简化到达”计划,即通过人脸识别验证乘客身份,加快安检速度和防止非法入境。

2020-10-15 09:52:43 390

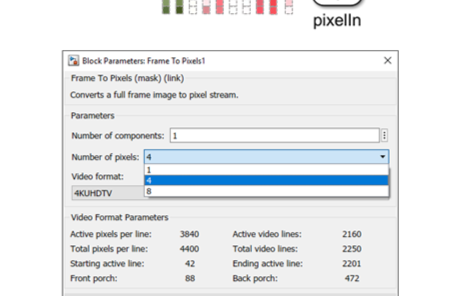

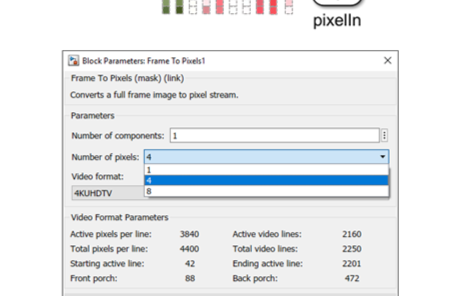

390 MathWorks宣布,随着 2019b 发行版的 MATLAB 和 Simulink 产品系列最近上市,Vision HDL Toolbox提供对在 FPGA 上处理高帧率 (HFR) 和高分辨率视频的原生多像素流处理支持。

2020-05-09 10:55:41 266

266

MathWorks宣布,HDLVerifier从现已上市的Release2019b开始提供对UniversalVerificationMethodology(UVM)的支持。

2020-03-07 14:29:17 752

752 上处理高帧率 (HFR) 和高分辨率视频的原生多像素流处理支持。视频、图像处理和 FPGA 设计工程师在处理 240fps 或更高分辨率的 4k 或 8k 视频时可以加快权衡表现和实现的探索和仿真速度。

2020-03-01 12:40:38 640

640 ASIC芯片一旦流片功能就无法改变,基本专片专用。而FPGA可配置特性就可以应用在功能会改变的场合,例如,原型验证,ASIC设计过程中会使用到FPGA来进行原型验证;功能升级,在产品中采用FPGA实现一些业内暂时还没成熟的解决方案,可以在后续功能变动时方便升级。

2019-08-25 10:40:01 6687

6687

采用fpga原型威廉希尔官方网站

验证asic设计,首先需要把asic设计转化为fpga设计。但asic是基于标准单元库,fpga则是基于查找表,asic和fpga物理结构上的不同,决定了asic代码需要一定

2019-07-23 08:07:00 1536

1536

)。日益增加的片上系统(SoC)复杂性和软件内容以及上市时间压力对高效验证平台的需求更加紧迫。Verification Continuum的全新增强型原生集成实现了所有验证引擎之间的性能提升,加快了复杂片上系统设计的上市。

2019-06-11 08:42:06 3905

3905 FPGA SoC通过融合FPGA和ASIC两者的元件,跨越了灵活性和性能之间的界限。但随着它们进入高安全性、任务关键型市场,它们也面临着与标准SoC相同的问题,包括在日益复杂的器件中快速传输越来越多的数据,以及在验证和调试中可能出现的一切棘手的问题。

2019-02-13 15:58:27 538

538 电子系统设计人员使用FPGA来实现他们的原型开发,利用器件的可编程能力验证硬件和软件。一旦设计准备好进行量产时,设计人员寻找某类ASIC以达到功耗、性能和成本目标,特别是,能够提供硬件平台和工具包的ASIC,支持目前采用了FPGA的设计

2017-10-14 10:18:11 4

4 UVM已经成为了一种高效率的、从模块级到系统级完整验证环境开发标准,其中一个关键的原则是UVM可以开发出可重用的验证组件。获得重用动力的一个方面表现为标准的仿真器和硬件加速之间的验证组件和环境的复用

2017-09-15 17:08:11 14

14 的连接、驱动器、监视器、仿真序列以及功能覆盖率的建立。 本文呈现出了一种使用UVM验证方法学构建基于高可配置性的高级微处理器总线架构(AMBA)的IP验证环境,其中会使用到Synopsys公司的AMBA VIP和Ruby脚本。该验证环境可以支持通过使用AMBA设计参数进行自

2017-09-15 14:37:34 6

6 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。

2017-02-11 12:46:11 2802

2802 基于UVM的CAN模块自验证方法_熊涛

2017-01-08 14:47:53 3

3 一种基于UVM的混合信号验证环境_耿睿

2017-01-07 21:39:44 1

1 基于UVM的CPU卡芯片验证平台_钱一文

2017-01-07 19:00:39 4

4 基于UVM的验证平台设计研究_王国军

2017-01-07 19:00:39 4

4 彻底地验证其片上系统(SoC)是否符合HDMI 2.0规范,从而加速批量生产的准备时间。这款用于HDMI 2.0的Cadence VIP支持各种主流逻辑模拟器、验证语言及包括UVM(Universal Verification Methodology)在内的方法学。

2013-09-27 16:19:08 714

714 本文描述ASIC验证方法和过程,有助于ASIC设计者对验证的认识。模拟是验证ASIC并产生测试矢量的唯一途径,设计者可以对ASIC芯片或者在ASIC应用系统中进行功能和时序模拟。

2012-05-24 09:32:47 23

23 本文描述ASIC验证方法和过程,有助于ASIC设计者对验证的认识。模拟是验证ASIC并产生测试矢量的唯一途径,设计者可以对ASIC芯片或者在ASIC应用系统中进行功能和时序模拟。

2012-05-24 09:32:47 27

27 MathWorks 近日宣布推出 HDL Coder,该产品 支持MATLAB 自动生成 HDL 代码,允许工程师利用广泛应用的 MATLAB 语言实现 FPGA 和 ASIC 设计。

2012-03-07 09:27:18 1823

1823

ASIC和FPGA具有不同的价值主张,在作出选择前必须仔细评估。两种种威廉希尔官方网站

对比。这里介绍了ASIC和FPGA 的优势与劣势。

2011-03-31 17:30:09 4810

4810

对ASIC设计进行FPGA原型验证时,由于物理结构不同,ASIC的代码必须进行一定的转换后才能作为FPGA的输入。 现代集成电路设计中,芯片的规模和复杂度正呈指数增加。尤其在ASIC设计流程中

2011-03-25 15:16:20 105

105 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。由于FPGA与ASIC在结构、性能上各不相同,ASIC是基于标准单元库,FPGA用的

2010-09-10 17:22:26 904

904 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,业界第一个基于SystemVerilog、通用开放的验证方法学;其基于事务交易级的方法学,基于Factory Pattern 的对象生

2010-07-04 11:43:22 7

7 means of Mentor’s advanced verification methodology (AVM) basedunified verification platform solution.The continuing growth o

2010-07-04 11:39:45 17

17 在现在复杂的ASIC 设计中,校验(Verification)是最大的瓶颈。随着先进的半导体工艺威廉希尔官方网站

不断前进,随之带来的是ASIC 设计规模和设计复杂度的飞速增长,这使得传统的软件仿真工具

2009-11-24 12:20:02 24

24 that dominates time scales. This book defines a methodology that helps minimize the time necessary to meet the verification requirements. It also takes

2009-07-22 14:39:21 37

37

电子发烧友App

电子发烧友App

评论