为什么要在芯片中配置GPIO呢 作为一种基础的控制接口,GPIO(General Purpose Input/Output)即通用输入输出端口,可用于控制数字设备。因为GPIO的应用广泛,如控制

2023-09-13 15:28:59 290

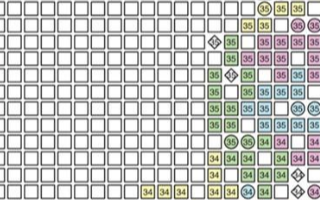

290 FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

2023-08-30 16:12:04 407

407

“全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 383

383

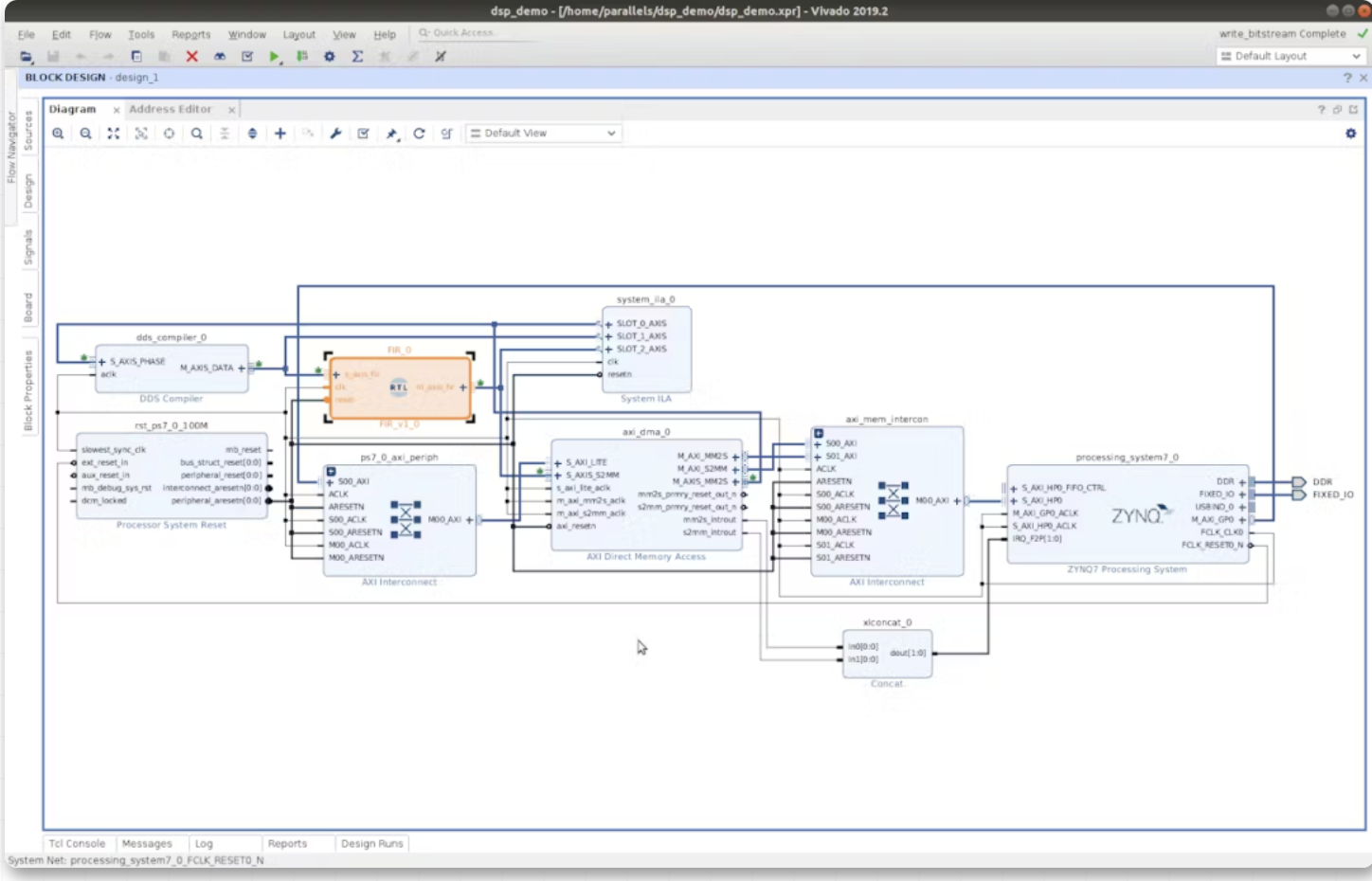

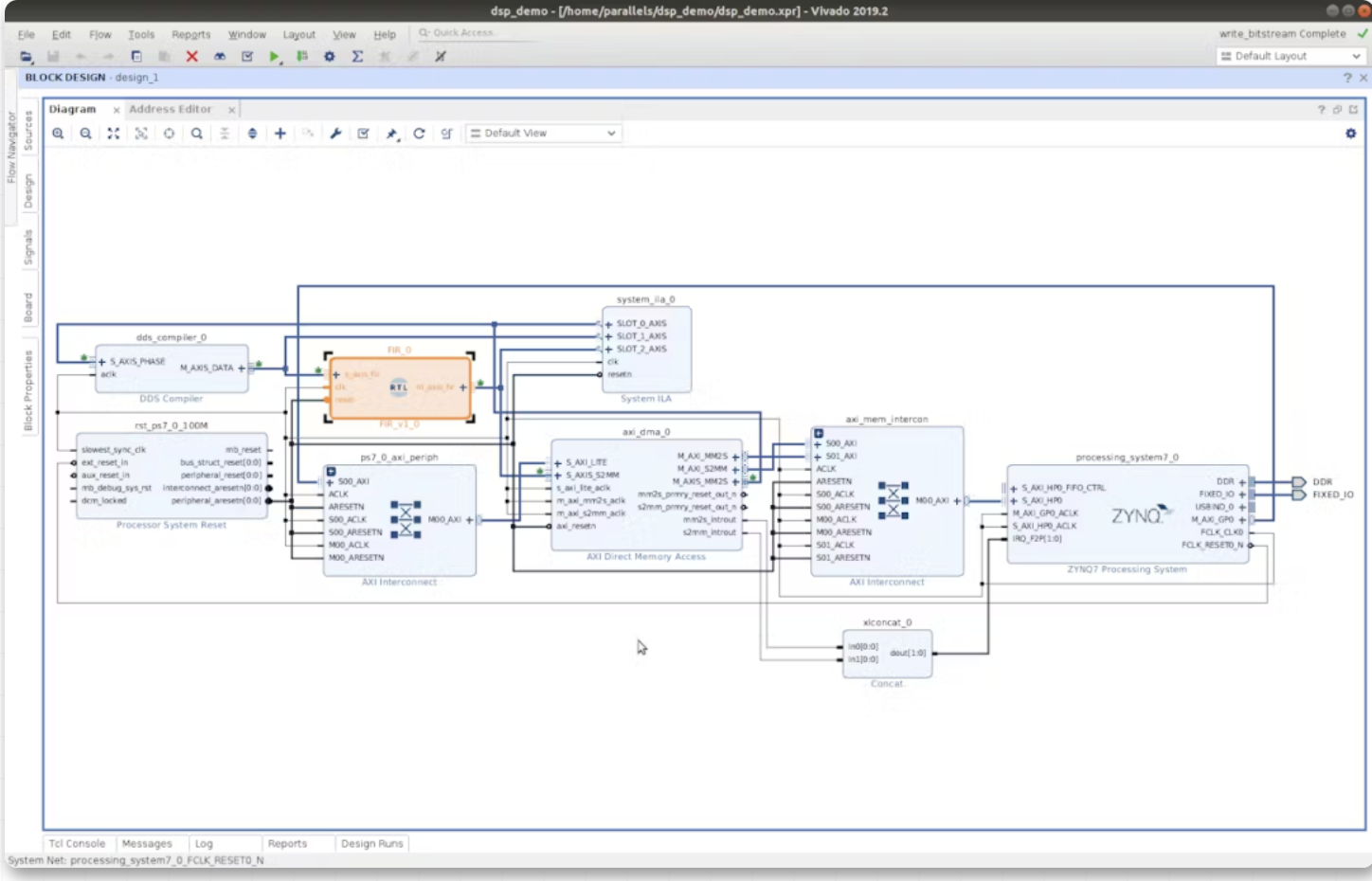

当在目标 FPGA 芯片中布局和布线时,首先在 Vivado 中确定时序要求.

2023-06-20 17:31:27 260

260

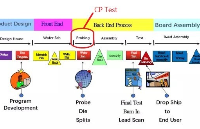

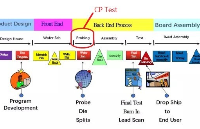

芯片中的CP测试是什么?让凯智通小编来为您解答~ ★芯片中的CP一般指的是CP测试,也就是晶圆测试(Chip Probing)。 一、CP测试是什么 CP测试在整个芯片制作流程中处于晶圆制造和封装

2023-06-10 15:51:49 2370

2370

FPGA CPLD同步设计若干问题浅析摘要:针对FPGA/CPLD同步设计过程中一些容易被忽视的问题进行了研究,分析了问题产生的原因、对可靠性的影响,并给出了解决方案。关键词:FPGA/CPLD

2009-04-21 16:42:01

如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-05-23 15:46:24 300

300

FPGA芯片说明书中,包含了可编程逻辑模块的数量、固定功能逻辑模块(如乘法器)的数目及存储器资源(如嵌入式RAM)的大小。FPGA芯片中还有很多其它的部分,但是以上指标通常是为特定应用选择和比较FPGA时,最重要的参考指标。

2023-01-09 09:28:46 674

674 关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

2022-12-13 13:20:06 801

801 而且现在的LUT都是4输入或者6输入,可以做成逻辑门的组合,跟普通的逻辑门个数肯定不会是一对一关系。今天我们来看下这个关系如果对应。

2022-11-11 09:06:23 629

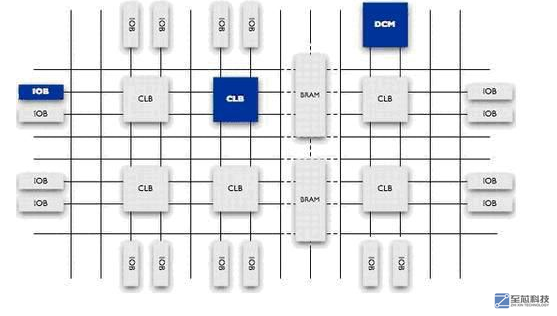

629 每一个系列的FPGA都有其相应的内部结构),FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

2022-10-25 09:01:05 1583

1583 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1112

1112 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 1988

1988 芯片中的CP一般指的是CP测试,也就是晶圆测试(Chip Probing)。

2022-07-12 17:00:57 11658

11658

BUCK电源芯片中自举电容的说明

2022-05-09 16:07:16 1

1 FPGA芯片本身就具有可以反复擦写的特性,允许FPGA开发者编写不同的代码进行重复编程,而FPGA可重构威廉希尔官方网站

正是在这个特性之上,采用分时复用的模式让不同任务功能的Bitstream文件使用FPGA芯片内部的各种逻辑资源

2022-04-26 10:38:54 2686

2686 (06)FPGA资源评估1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA资源评估5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 FPGA-SoC芯片中EDAC模块的设计与实现(深圳市宇衡源电源威廉希尔官方网站

)-该文档为FPGA-SoC芯片中EDAC模块的设计与实现简介文档,是一份还算不错的参考文档,感兴趣的可以下载看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 FPGA_ASIC-S698MSoC芯片中EDAC模块的设计与实现(第四届星载电源威廉希尔官方网站

学术研讨会)-该文档为FPGA_ASIC-S698MSoC芯片中EDAC模块的设计与实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-15 11:05:19 6

6 是最佳的,然后通过使用适当的I/O和时钟缓冲器来访问这些时钟路由资源。该章节包括: 时钟缓冲选择考虑 时钟输入管脚 1.时钟缓冲器选择考虑 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求

2021-03-22 10:16:18 4052

4052

FPGA 由6 部分组成, 分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM 、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

2021-02-25 17:55:37 12

12 在使用 FPGA 过程中,通常需要对资源做出评估,下面简单谈谈如何评估 FPGA 的资源。 FF 和 LUT 的数目:这个在写出具体代码之前,初学者通常没法估算,但资深 FPGA 工程师会估算出一

2020-12-28 07:59:00 8

8 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

2020-12-25 17:34:39 8

8 结合Xilinx、Altera 等公司的FPGA 芯片,简要罗列一下FPGA 内部的资源或专用模块,并简要说明这些资源的一些作用或用途。(至少列出5 项,越多越好)

2020-12-25 17:34:00 16

16 在FPGA中block ram是很常见的硬核资源,合理的利用这些硬件资源一定程度上可以优化整个设计,节约资源利用率,充分开发FPGA芯片中的潜在价值,本文结合安路科技FPGA做简单总结,说明基本原理。

2020-12-24 14:28:09 722

722 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

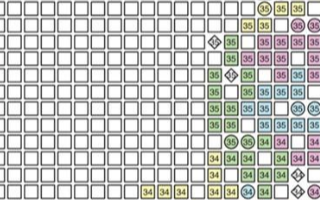

13 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA中

2020-12-09 14:49:03 20

20 在本辅导教材中,将重点讲解如何将一个设计项目物理地实现于FPGA 芯片中。我们将展示如何用手工的方法选择器件封装的引脚,并且把这些引脚用做电路的输入和输出信号,此外还将描述如何使用Quartus II 编程器模块把编译完的电路传送到所选择的FPGA芯片中。

2020-10-27 16:26:00 20

20 虽然很多 FPGA 工程师都是写代码,但是作为硬件编程工程师,如果不熟悉 FPGA 的底层资源和架构,是很难写出高质量的代码——至少很难写出复杂逻辑的高质量代码,也很难站在系统的层面去考虑芯片的选型等问题。那熟悉 FPGA 架构,首先最主要的一点,我们先来了解 FPGA 的 IO。

2020-07-16 17:53:02 8500

8500

FPGA的基本组成有:可编程I\O单元、基本可编程逻辑单元、内嵌RAM块、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

2020-06-04 10:55:16 15183

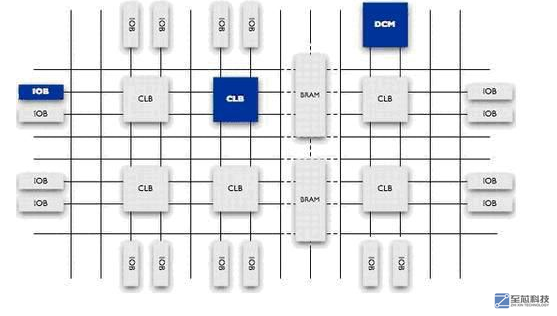

15183 FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用

2019-12-19 07:08:00 1151

1151 FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。

2019-11-29 07:03:00 2371

2371 FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。

2019-11-25 07:07:00 906

906 FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。

2019-11-21 07:03:00 1669

1669 在FPGA高速AD采集设计中,PCB布线差会产生干扰。今天小编为大家介绍一些布线解决方案。

2019-03-07 14:52:24 5872

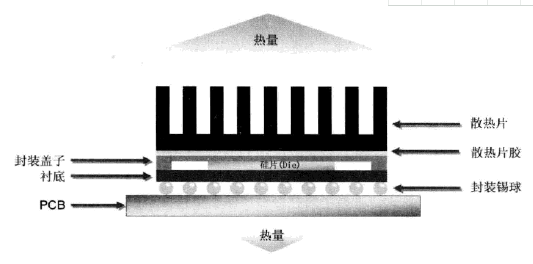

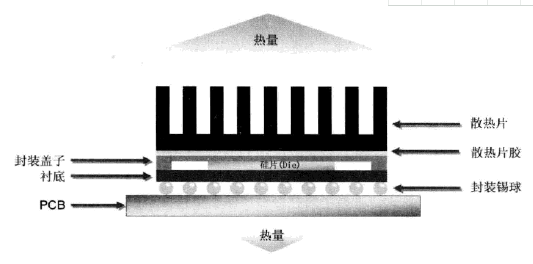

5872 ALTERA的FPGA分为商用级(commercial)和工业级(induatrial)两种,商用级的芯片可以正常工作的结温范围为0~85摄氏度,而工业级芯片的范围是-40~100摄氏度。在实际电路中,我们必须保证芯片的结温在其可以承受的范围之内。

2019-02-28 14:41:50 6761

6761

在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

2019-02-15 15:09:05 3362

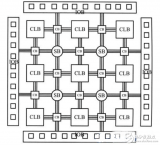

3362 现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。

2018-10-22 11:00:43 5048

5048 FPGA以计算速度快、资源丰富、可编程著称,之前一直应用于高速数字信号领域和ASIC验证。随着逻辑资源的丰富和编程工具的改进,FPGA在机器学习和硬件加速上得到越来越多的重视,目前数据中心已经大量

2018-07-31 10:34:35 934

934

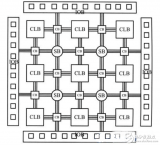

(ASIC型)模块。如图所示,FPGA芯片主要由7部分组成,分别为:可编程输入输出单元(IOB)、基本可编程逻辑单元(CLB)、完整的时钟管理(DCM)、嵌入式块RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。 1.可编程输入输出单元(IOB) 可编程

2018-05-25 14:11:47 8307

8307

。FPGA芯片主要由7部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

2018-01-15 14:34:41 11461

11461

FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

2018-01-02 15:46:40 26006

26006

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 74系列芯片中文资料下载

2017-10-13 09:58:45 68

68 DS1302芯片中文资料

2017-09-21 08:15:52 59

59 BHL2000芯片中文资料

2017-02-08 02:16:12 12

12 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 电池监测芯片中稳压模块的设计,很不错的资料,值得参考。

2016-09-18 18:05:07 4

4 赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19450

19450

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的

2013-01-06 16:12:44 1533

1533 电子发烧友网: 本文主要为大家浅析Altera公司 28nm Stratix V FPGA。Altera公司公布了其28nm Stratix V FPGA的性能参数指标,具体参数如下表所示。该款芯片发售日期为2011年一季度。 与Altera St

2012-08-10 10:07:04 7120

7120 MCS-51芯片中文资料

2008-01-07 10:58:27 53

53

74系列芯片中文资料下载

2007-12-17 22:54:30 8305

8305

电子发烧友App

电子发烧友App

评论